255

Chapter 18 Timebase Counter

5.Operation

■ Watchdog reset when main clock operating

Although no oscillation stabilization wait is required in this case, the specified wait time is generated

automatically.

5.3 Recovering from Stop Mode via an Interrupt

■ When changing from main PLL operation to stop mode with the main clock oscillation halted

(STCR.OSCD[2:1]=“11”):

The main oscillation circuit generates the selected oscillation stabilization time automatically.

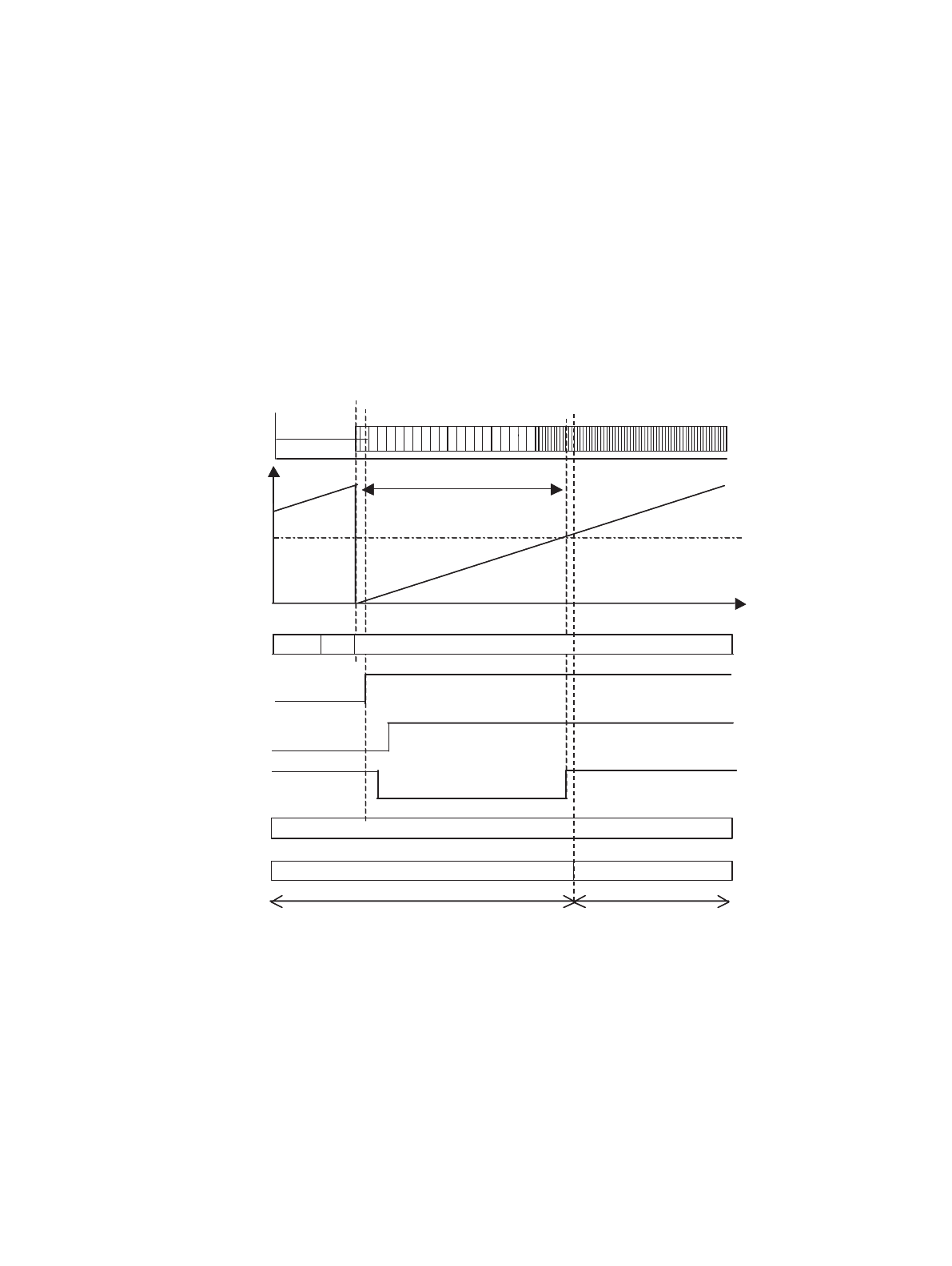

Figure 5-3 Recovering from Stop Mode with the Main Clock Halted to

Main PLL Operation via an Interrupt

(1) Enabled interrupt is generated (end stop mode)

(2) The timebase counter is cleared automatically and then starts counting.

(3) Oscillation stabilization wait time (specified value)

(Set the interval time beforehand to provide an adequate oscillation stabilization wait time.)

(4) Interval time for timebase counter

(5) Main PLL operation

(5)

“

000h

Using the time-base timer to wait

main PLL lock

Example main PLL

startup

13

2

Time-base

counter count

(1)

Clear the time-base counter.

(CTBR)

Enable main PLL (PLL1EN)

Enable the time base timer

interrupt request. (PLL1EN)

Time base timer interrupt

request (PLL1EN)

(2)

Setting or switching

the main PLL value

(PLL1S[2:0])

Clock switching (CLKS[1:0])

Operation of the divided- by-2 main clock

Operation of the PLL clock

Provide a sufficient oscillation

stabilization wait time.

Time

(8)

(5)

(8)

(5)

(6)

(7)

(9)

(10)

(3)

(4)

(9)

“A5”

“00”

“111”

“10”

“5A”