705

Chapter 34 CAN Controller

2.Register Description

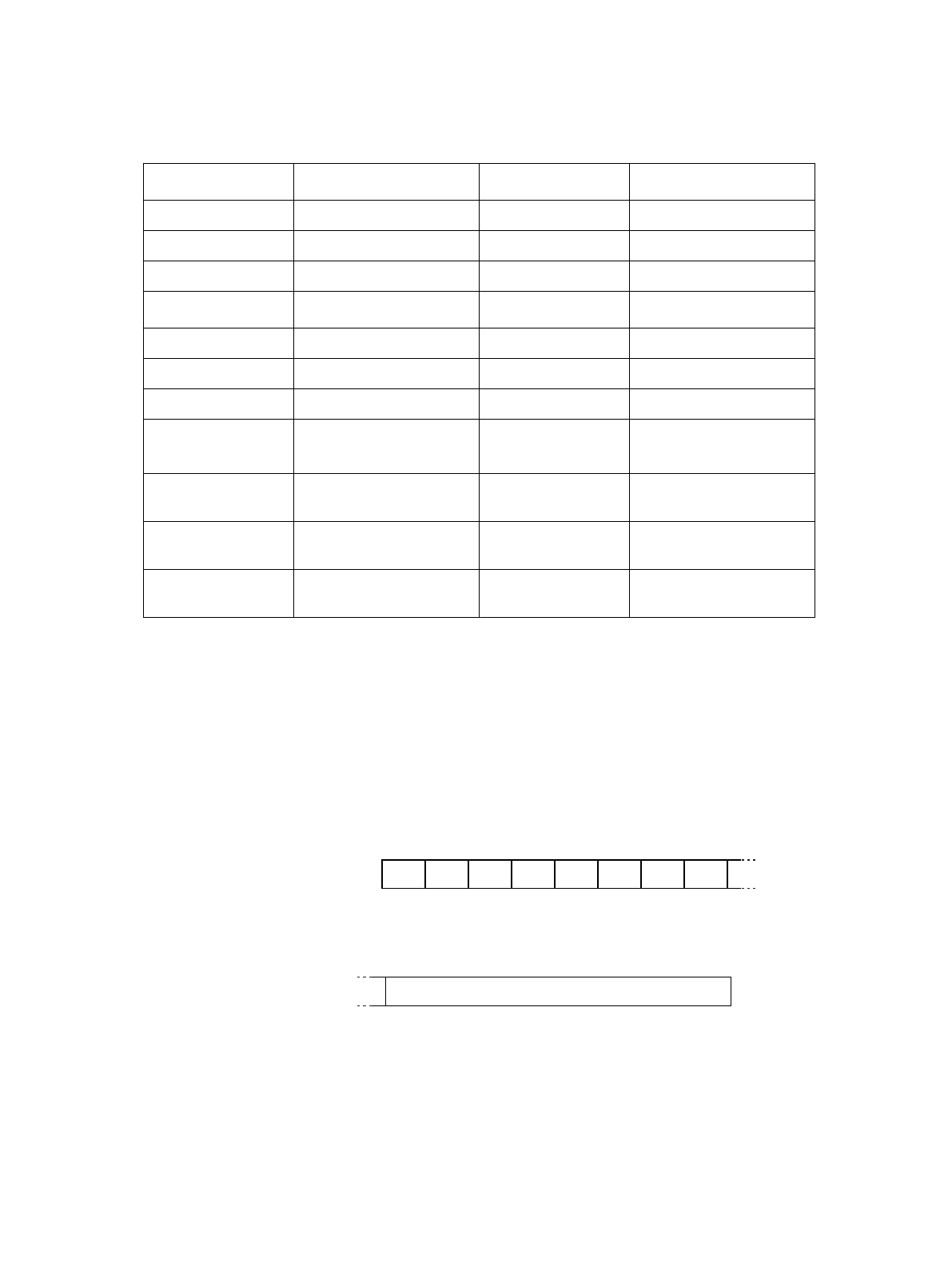

Figure 2-3 IF1 and IF2 Message Interface Register Sets

■ IFx Command Request Registers (IFxCREQ)

A message transfer is started as soon as the CPU has written the message number to the Command Request

Register. With this write operation the CPU is notified that a transfer is in progress. If a CPU access to the

CAN happens while the transfer is in progress then this access is delayed until the transfer has finished. After

3to6CAN_CLK periods, the transfer between the Interface Register and the Message RAM has completed

and the upcoming CPU access is executed.

Address IF1 Register Set Address IF2 Register Set

CAN Base + 0x10 IF1 Command Request CAN Base + 0x40 IF2 Command Request

CAN Base + 0x12 IF1 Command Mask CAN Base + 0x42 IF2 Command Mask

CAN Base + 0x14 IF1 Mask 2 CAN Base + 0x44 IF2 Mask 2

CAN Base + 0x16 IF1 Mask 1 CAN Base + 0x46 IF2 Mask 1

CAN Base + 0x18 IF1 Arbitration 2 CAN Base + 0x48 IF2 Arbitration 2

CAN Base + 0x1A IF1 Arbitration 1 CAN Base + 0x4A IF2 Arbitration 1

CAN Base + 0x1C IF1 Message Control CAN Base + 0x4C IF2 Message Control

CAN Base + 0x20

CAN Base + 0x32

IF1 Data A1

CAN Base + 0x50

CAN Base + 0x62

IF2 Data A1

CAN Base + 0x22

CAN Base + 0x30

IF1 Data A2

CAN Base + 0x52

CAN Base + 0x60

IF2 Data A2

CAN Base + 0x24

CAN Base + 0x36

IF1 Data B1

CAN Base + 0x54

CAN Base + 0x66

IF2 Data B1

CAN Base + 0x26

CAN Base + 0x34

IF1 Data B2

CAN Base + 0x56

CAN Base + 0x64

IF2 Data B2

BUSY res res res res res res res

⇐ Bit no.

Read/write ⇒

(R/(W)) (R) (R) (R) (R) (R) (R) (R)

Default value⇒

(0) (0) (0) (0) (0) (0) (0) (0)

IFx Command Request Register high byte

Address : Base + 0x10

H &

Base + 0x40

H

15 14 13 12 11 10 9 8

IFxCREQH

Message Number

⇐ Bit no.

Read/write ⇒

(R/W) (R/W) (R/W) (R/W) (R/W) (R/W) (R/W) (R/W)

Default value⇒

(0) (0) (0) (0) (0) (0) (0) (1)

Address :

Base + 0x

11H &

Base + 0x

41H

765432 10

IFxCREQL

IFx Command Request Register low byte