236

Chapter 16 Clock Supervisor

4.Operation Modes

■ Stop mode

If RC-oscillator, main clock and sub-clock supervisors are enabled, they will be automatically disabled at

transition into stop mode. The corresponding enable bits in the clock supervisor control register remain

unchanged. So after wake-up from stop mode the RC-oscillator and the clock supervisors will be enabled again. If

the corresponding enable bits are set to ’0’, the RC-oscillator and the clock supervisors will stay disabled after

wake-up from stop mode.

• The RC-oscillator is enabled immediately after wake-up from stop mode.

• The main clock supervisor is enabled after the ’oscillation stabilisation wait time’ with the rising edge of the

signal OSC_STAB or in case the main clock is missing after wake-up from stop mode, after the ’main clock

timeout’ (TO_MCLK) from the timeout counter. The timeout counter is clocked with RC-oscillation clock.

• The sub-clock supervisor is enabled after the ’sub-clock timeout’ (TO_SCLK) from the timeout counter which is

clocked with the RC-oscillation clock.

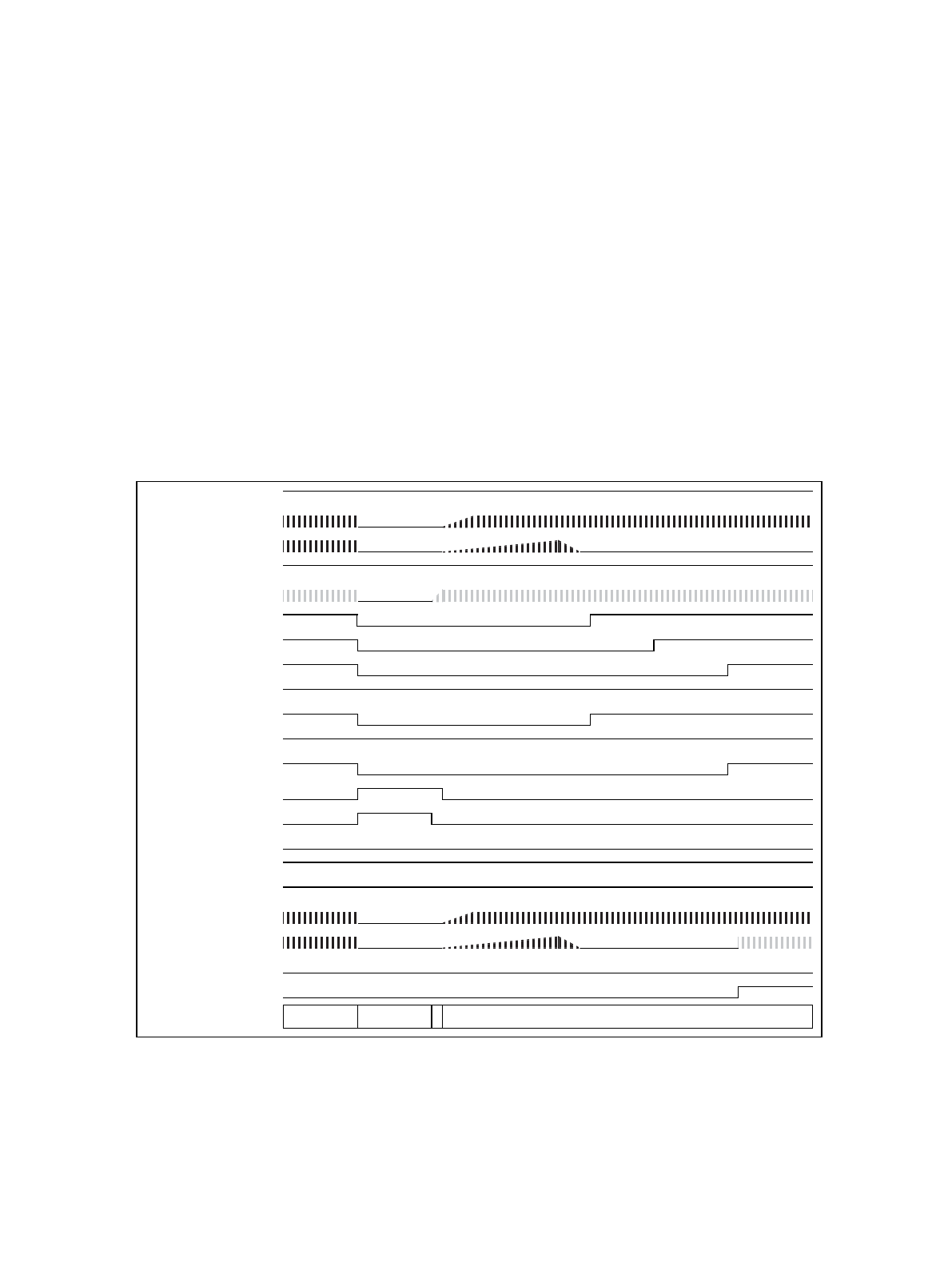

Figure 4-11 Timing Diagram: Waking up from stop mode

PONR

MCLK

SCLK

RC_CLK

OSC_STAB

MSVE

MSEN

SSVE

SSEN

MCLK_STBY

SCLK_STBY

TO_MCLK

TO_SCLK

EXT_RST

EXT_RST_OUT

MCLK_OUT

SCLK_OUT

MCLK_MISSING

SCLK_MISSING

SRST

RCE

Clock Mode

Main Stop Main

Sub