733

Chapter 35 Free-Run Timer

1.Overview

Chapter 35 Free-Run Timer

1. Overview

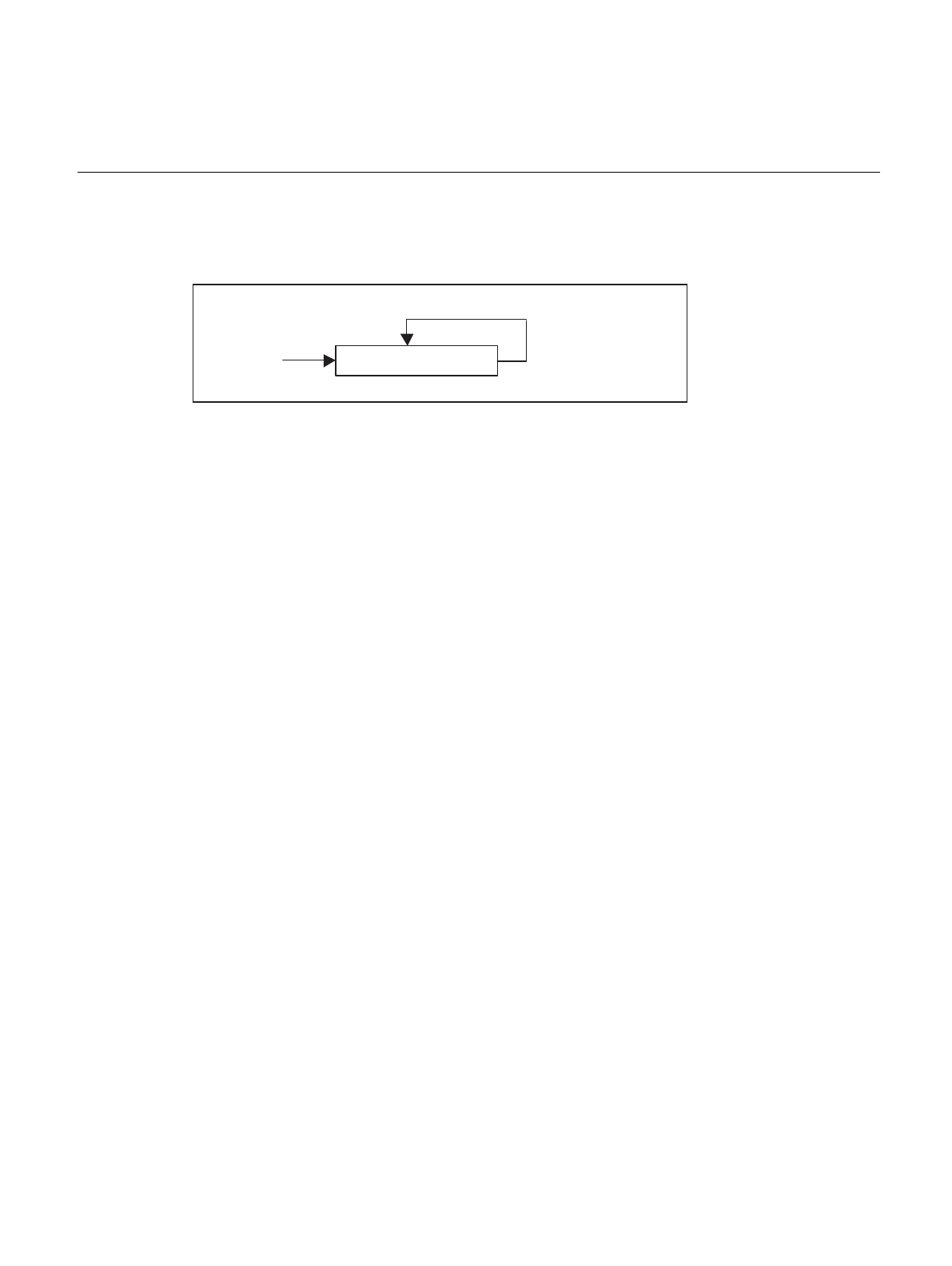

The free-run timer consists of a 16-bit timer (up counter) and control circuits.

The free-run timer can be used with the input capture and the output compare.

2. Features

• Format: 16-bit up counter

• Quantity: 8 (free-run timer 0 up to free-run timer 7)

• Clock source: 4 internal clocks (1/4, 1/16, 1/32, and 1/64 of CLKP)

• External clock (CK)

• Clear factor of the count:

• Software

• Reset

• Compare-match (match of the compare-register value and the count value of the free-run timer)

• Operation start/stop: operations can be started/stopped with software.

• Interrupt:

• Overflow interrupt

• An interrupt generated when the compare clear register value and the count value of the free-run timer

match.

• Count value: Readable/writable (write is only possible when the counting stops)

• Others: Operates from immediately after reset.

• Free Run Timer to ICU/OCU mapping:

• Free-run timer 0 and input capture 0/1 co-operate

• Free-run timer 1 and input capture 2/3 co-operate

• Free-run timer 2 and output compare 0/1 co-operate

• Free-run timer 3 and output compare 2/3 co-operate

• Free-run timer 4 and input capture 4/5 co-operate

• Free-run timer 5 and input capture 6/7 co-operate

• Free-run timer 6 and output compare 4/5 co-operate

• Free-run timer 7 and output compare 6/7 co-operate

or

Clear

Internal clock

or

External clock

OverflowUp counter