718

Chapter 34 CAN Controller

2.Register Description

These registers hold the IntPnd bits of the 32 Message Objects. By reading out the IntPnd bits, the CPU can

check for which Message Object an interrupt is pending. The IntPnd bit of a specific Message Object can be

set/reset by the CPU via the IFx Message Interface Registers or by the Message Handler after reception or

after a successful transmission of a frame. This will also affect the value of IntId in the Interrupt Register.

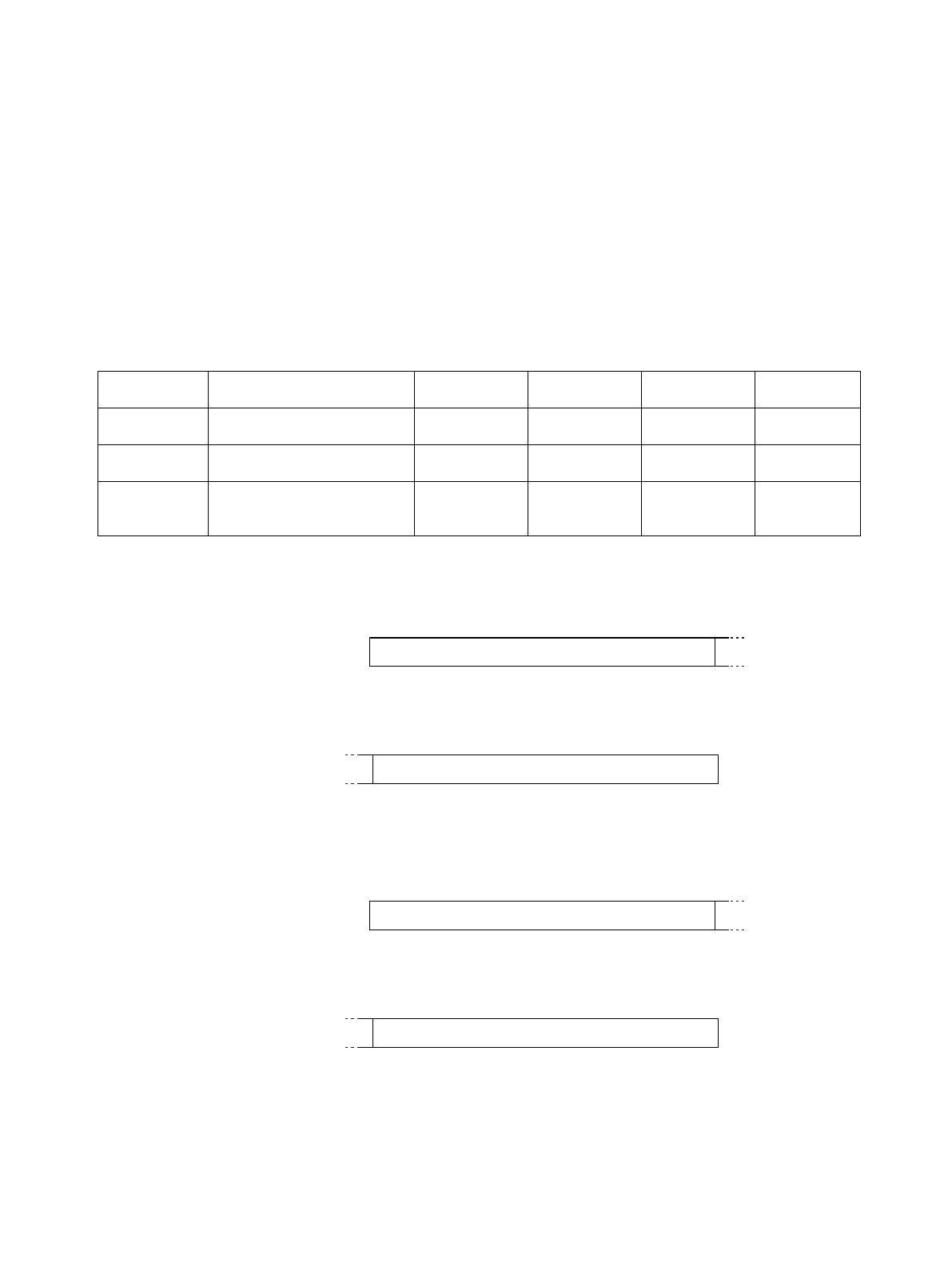

If more than 32 message buffers are implemented, the following table gives an overview about the additional

flags:

Table 2-3 Additional flags when more than 32 message buffers exist

■ Message Valid Registers (MSGVAL)

1 This message object is the source of an interrupt.

addr+0 addr+1 addr+2 addr+3

INTPND 4 & 3 IntPnd 64-33 (address 0xA4) IntPnd64-57 IntPnd56-49 IntPnd48-41 IntPnd40-33

INTPND 6 & 5 IntPnd 96-65 (address 0xA8) IntPnd96-89 IntPnd88-81 IntPnd80-73 IntPnd72-65

INTPND 8 & 7 IntPd 128-97 (address 0xAC)

IntPnd128-

121

IntPnd120-

113

IntPnd112-

105

IntPnd104-

97

MsgVal32-25

⇐ Bit no.

Read/write ⇒

(R) (R) (R) (R) (R) (R) (R) (R)

Default value⇒

(0) (0) (0) (0) (0) (0) (0) (0)

Message Valid Register 2 high byte

Address : Base + 0xB0

H

15 14 13 12 11 10 9 8

MSGVAL2H

MsgVal24-17

⇐ Bit no.

Read/write ⇒

(R) (R) (R) (R) (R) (R) (R) (R)

Default value⇒

(0) (0) (0) (0) (0) (0) (0) (0)

Address :

Base + 0x

B1H

765432 10

MSGVAL2L

Message Valid Register 2 low byte

MsgVal16-9

⇐ Bit no.

Read/write ⇒

(R) (R) (R) (R) (R) (R) (R) (R)

Default value⇒

(0) (0) (0) (0) (0) (0) (0) (0)

Message Valid Register 1 high byte

Address : Base + 0xB2

H

15 14 13 12 11 10 9 8

MSGVAL1H

MsgVal8-1

⇐ Bit no.

Read/write ⇒

(R) (R) (R) (R) (R) (R) (R) (R)

Default value⇒

(0) (0) (0) (0) (0) (0) (0) (0)

Address :

Base + 0x

B3H

765432 10

MSGVAL1L

Message Valid Register 1 low byte