340

Chapter 26 DMA Controller

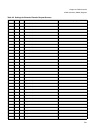

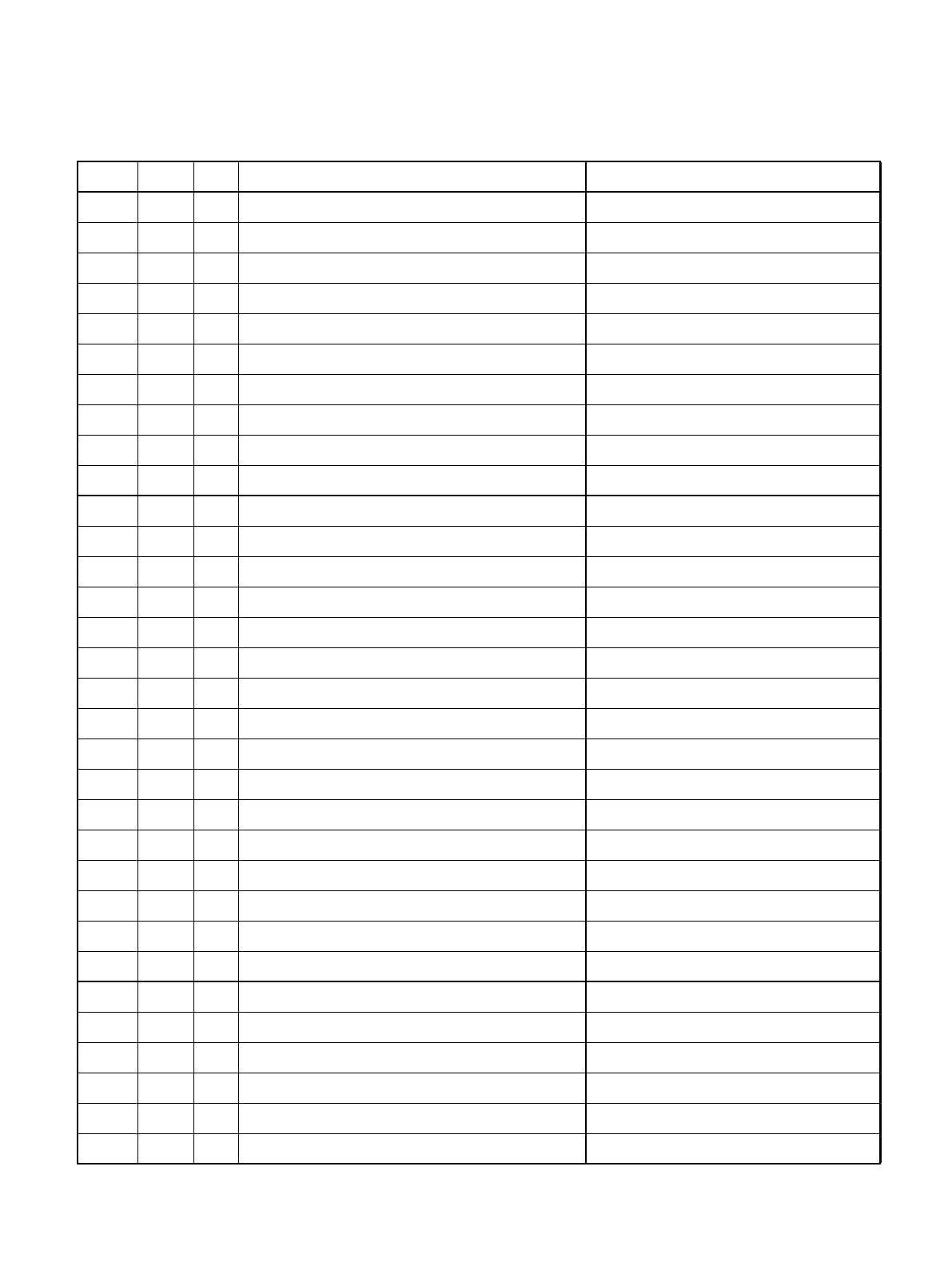

2.DMA Controller (DMAC) Registers

10110 0010 38 Reload Timer 6 -

10111 0010 39 Reload Timer 7 -

11000 0010 40 Free Run Timer 0 -

11001 0010 41 Free Run Timer 1 -

11010 0010 42 Free Run Timer 2 -

11011 0010 43 Free Run Timer 3 -

11100 0010 44 Free Run Timer 4 -

11101 0010 45 Free Run Timer 5 -

11110 0010 46 Free Run Timer 6 -

11111 0010 47 Free Run Timer 7 -

10000 0011 48 USART (LIN) 0 RX available

10001 0011 49 USART (LIN) 0 TX -

10010 0011 50 USART (LIN) 1 RX available

10011 0011 51 USART (LIN) 1 TX -

10100 0011 52 USART (LIN) 2 RX available

10101 0011 53 USART (LIN) 2 TX -

10110 0011 54 USART (LIN) 3 RX available

10111 0011 55 USART (LIN) 3 TX -

11000 0011 56 USART (LIN, FIFO) 4 RX available

11001 0011 57 USART (LIN, FIFO) 4 TX -

11010 0011 58 USART (LIN, FIFO) 5 RX available

11011 0011 59 USART (LIN, FIFO) 5 TX -

11100 0011 60 USART (LIN, FIFO) 6 RX available

11101 0011 61 USART (LIN, FIFO) 6 TX -

11110 0011 62 USART (LIN, FIFO) 7 RX available

11111 0011 63 USART (LIN, FIFO) 7 TX -

10000 0100 64 USART (LIN) 8 RX available

10001 0100 65 USART (LIN) 8 TX -

10010 0100 66 USART (LIN) 9 RX available

10011 0100 67 USART (LIN) 9 TX -

10100 0100 68 USART (LIN) 10 RX available

10101 0100 69 USART (LIN) 10 TX -

Table 2-2 Settings for Extended Transfer Request Sources

IS EIS RN Function Transfer stop request