648

Chapter 32 USART (LIN / FIFO)

7.USART Operation

TXE) and reception (SCR04: RXE). If each of the operations is disabled, stop it as follows:

• If reception operation is disabled during reception (data is input to the reception shift register), finish frame

reception and read the received data of the reception data register (RDR04). Then stop the reception

operation.

• If the transmission operation is disabled during transmission (data is output from the transmission shift

register), wait until there is no data in the transmission data register (TDR04) before stopping the

transmission operation.

7.1 Operation in Asynchronous Mode (Op. Modes 0 and 1)

When USART is used in operation mode 0 (normal mode) or operation mode 1 (multiprocessor mode), the

asynchronous transfer mode is selected.

■ Transfer data format

Generally each data transfer in the asynchronous mode operation begins with the start bit (low-level on bus)

and ends with at least one stop bit (high-level). The direction of the bit stream (LSB first or MSB first) is

determined by the BDS-Bit of the Serial Status Register (SSR04). The parity bit (if enabled) is always placed

between the last data bit and the (first) stop bit.

In operation mode 0 the length of the data frame can be 7 or 8 bits, with or without parity, and 1 or 2 stop bits.

In operation mode 1 the length of the data frame can be 7 or 8 bits with a following address-/data-selection bit

instead of a parity bit. 1 or 2 stop bits can be selected.

The calculation formula for the bit length of a transfer frame is:

Length = 1 + d + p + s

(d = number of data bits [7 or 8], p = parity [0 or 1], s = number of stop bits [1 or 2]

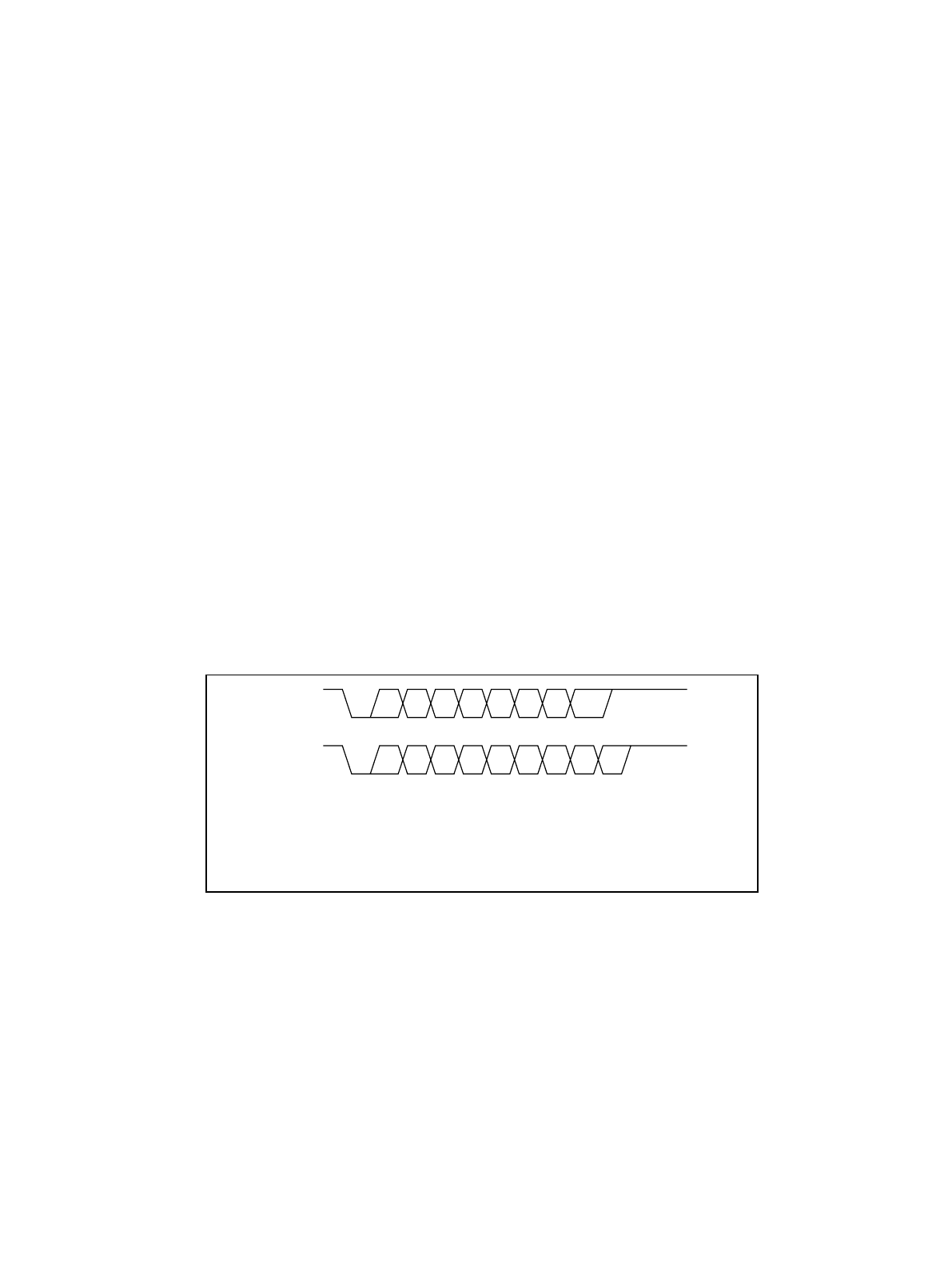

Figure 7-1 Transfer data format (operation modes 0 and 1)

(Note) If BDS-Bit of the Serial Status Register (SSR04) is set to "1" (MSB first), the bit stream processes as:

D7, D6, ... , D1, D0, (P).

During Reception both stop bits are detected, if selected. But the Reception data register full (RDRF) flag will

go "1" at the first stop bit. The bus idle flag (RBI of ECCR04) goes "1" after the second stop bit if no further

start bit is detected. (The second stop bit belongs to "bus activity", although it is just mark level.)

■ Transmission Operation

If the Transmission Data Register Empty (TDRE) flag bit of the Serial Status Register (SSR04) is "1",

transmission data is allowed to be written to the Transmission Data Register (TDR04). When data is written,

the TDRE flag goes "0". If the transmission operation is enabled by the TXE-Bit ("1") of the Serial Control

Register (SCR04), the data is written next to the transmission shift register and the transmission starts at the

next clock cycle of the serial clock, beginning with the start bit. Thereby the TDRE flag goes "1", so that new

data can be written to the TDR04.

Operation mode 0

Operation mode 1

ST D0 D1 D2 D3 D4 D5 D6 D7/P SP SP

***

ST D0 D1 D2 D3 D4 D5 D6 D7 A/D SP

* D7 (bit 7) if parity is not provided and data length is 8 bits

P (parity) if parity is provided and data length is 7 bits

** only if SBL-Bit of SCR is set to 1

ST: Start Bit SP: Stop Bit A/D: Address/data selection bit in mode 1 (multiprocessor mode)