299

Chapter 23 Sub Oscillation Stabilisation Timer

1.Overview

Chapter 23 Sub Oscillation Stabilisation Timer

1. Overview

The sub oscillation stabilisation timer is a 15-bit counter that is counted up with the subclock. This timer does

not affect the selection/dividing setting of the MCU operating clock.

This timer is used to acquire subclock oscillation stability wait time if the subclock oscillation is resumed mainly

when the subclock oscillation is stopped while the main clock is in operation.

This timer is can be used for acquiring sub clock oscillation stability wait time to resume sub clock oscillation

after the sub clock oscillation has been stopped (OSCCR.OSCDS2=1) while the RC oscillator is being

operated.

2. Features

• Type : 15-bit free run counter

• Quantity : 1

• Clock source : Subclock (source oscillation) --- Period = 1/F

CL-SUB

= 1/32.768kHz

• Interval time : 4 types

Period = 2

10

/F

CL-SUB

, 2

13

/F

CL-SUB

, 2

14

/F

CL-SUB

, 2

15

/F

CL-SUB

,

(31.25ms, 0.25s, 0.50s, 1.00s)

• Timer clear cause: (Software, overflow, reset (INIT))

• Interrupt : clock interrupt (interval interrupt)

• Count value : Cannot read and write (Clear only)

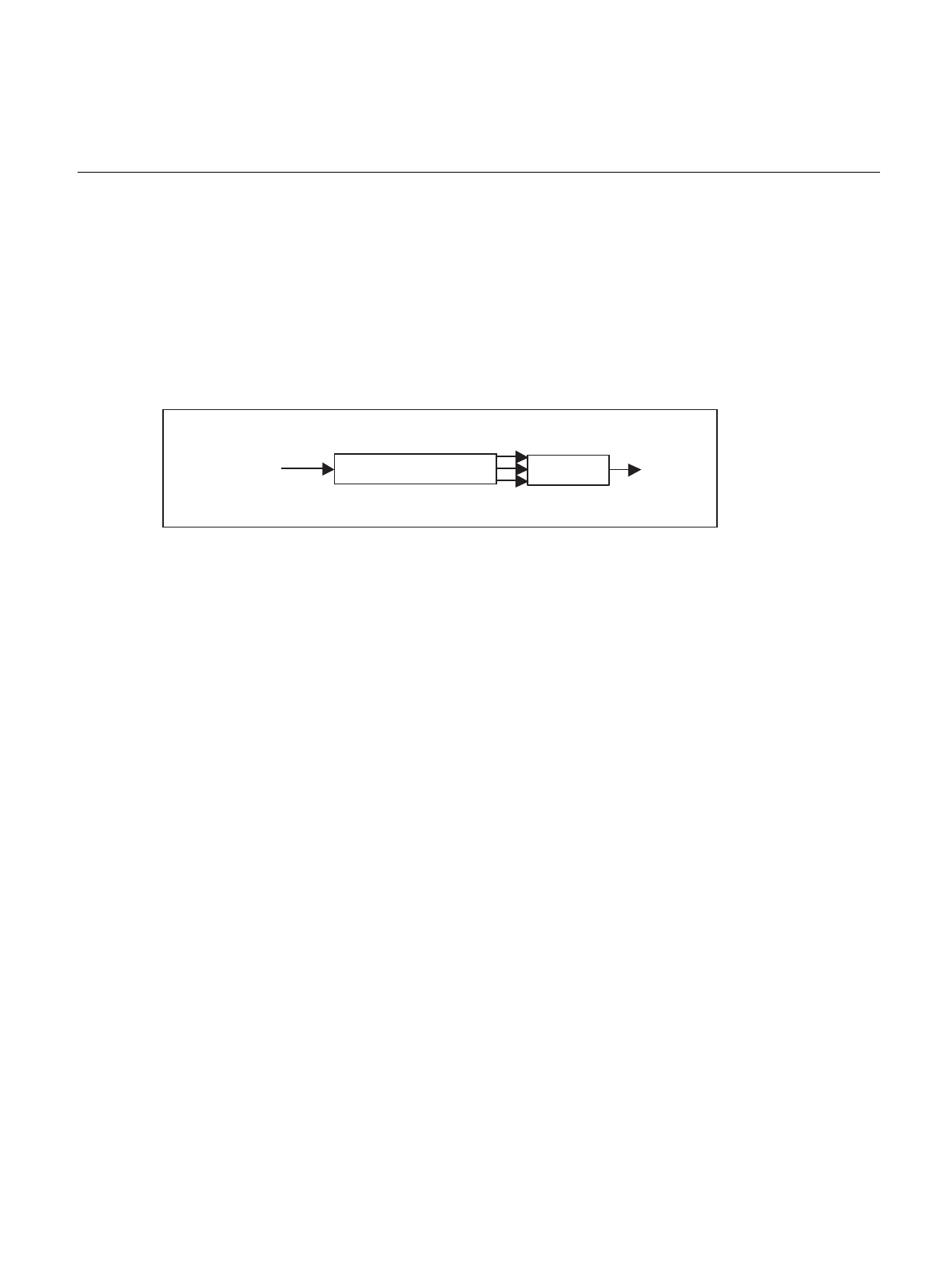

Sub clock

(Source oscillation)

Up-counter

Selector

Interrupt