701

Chapter 34 CAN Controller

2.Register Description

■ Function of the Error Counter (ERRCNT)

■ Bit Timing Register (BTR)

[bit15] RP Receive Error Passive

0 The Receive Error Counter is below the error passive level.

1 The Receive Error Counter has reached the error passive level as defined in the

CAN Specification.

[bit14 - bit8] REC6-0 Receive Error Counter

Actual state of the Receive Error Counter. Values between 0 and 127.

[bit7 - bit0] TEC7-0 Transmit Error Counter

Actual state of the Transmit Error Counter. Values between 0 and 255.

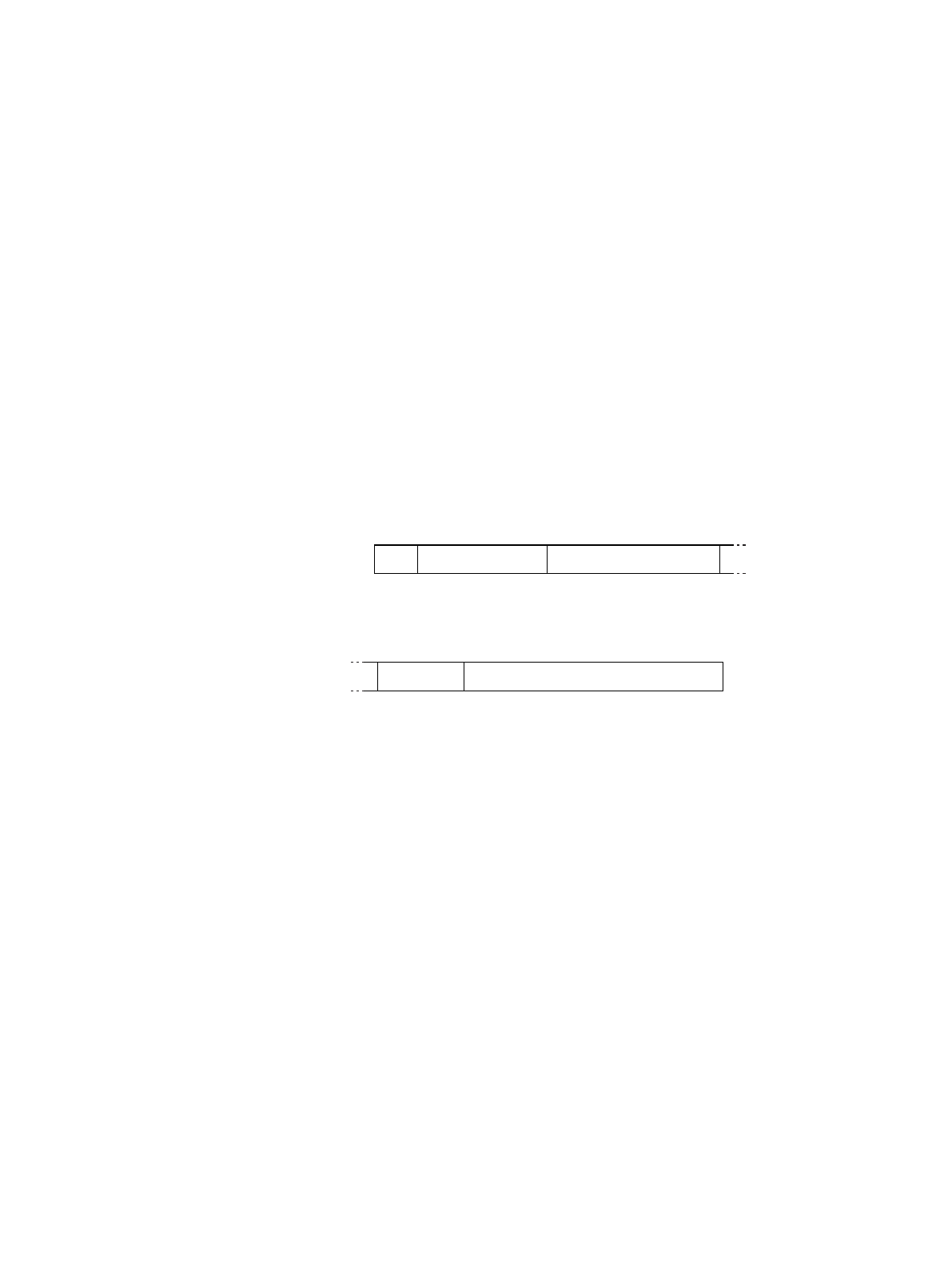

res TSeg2

TSeg1

⇐ Bit no.

Read/write ⇒

(R) (R/W) (R/W) (R/W) (R/W) (R/W) (R/W) (R/W)

Default value⇒

(0) (0) (1) (0) (0) (0) (1) (1)

Bit Timimg Register high byte

Address : Base + 0x06

H

15 14 13 12 11 10 9 8

BTRH

SJW BRP

⇐ Bit no.

Read/write ⇒

(R

/W

) (R/W) (R/W) (R/W) (R/W) (R/W) (R

/W

)(R

/W

)

Default value⇒

(0) (0) (0) (0) (0) (0) (0) (1)

Address :

Base + 0x

07H

765432 10

BTRL

Bit Timing Register low byte