517

Chapter 31 External Bus

2.External Bus Interface Registers

In areas for which a burst length other than the single access is set, continuous burst access is performed within

the address boundary determined by the burst length only when prefetch access is performed or data having a

size exceeding the bus width is read.

Setting of 2 bursts or less as the maximum burst length in the bus width 16-bit area is recommended.

RDY input is ignored in areas for which any burst length other than the single access is set.

[Bit 7] SREN (ShaRed Enable)

This bit sets enabling or disabling of sharing of each chip select area by BRQ/BGRNT as indicated in the

following table.

In areas where sharing is enabled, chip select output (CSn) is set to high impedance while the bus is open

(during BGRNT=Low output). In areas where sharing is disabled, chip select output (CSn) is not set to high

impedance even though the bus is open (during BGRNT=Low output).

Access strobe output (AS, BAA, RD, WR0, WR1, WR2, WR3, WR, MCLK, MCLKE) is set to high impedance only

if sharing of all areas enabled by CSER is enabled.

[Bit 6] PFEN (PreFetch Enable)

This bit sets enabling and disabling of prefetching of each chip select area as indicated in the following table.

When reading from an area for which prefetching is enabled, the subsequent address is read in advance and

stored in the built-in prefetch buffer. When the stored address is accessed from the internal bus, the lookahead

data in the prefetch buffer is returned without performing external access.

For more information, see Section 8. "Prefetch Operation".

[Bit 5] WREN(WRite Enable)

This bit sets enabling and disabling of writing to each chip select area.

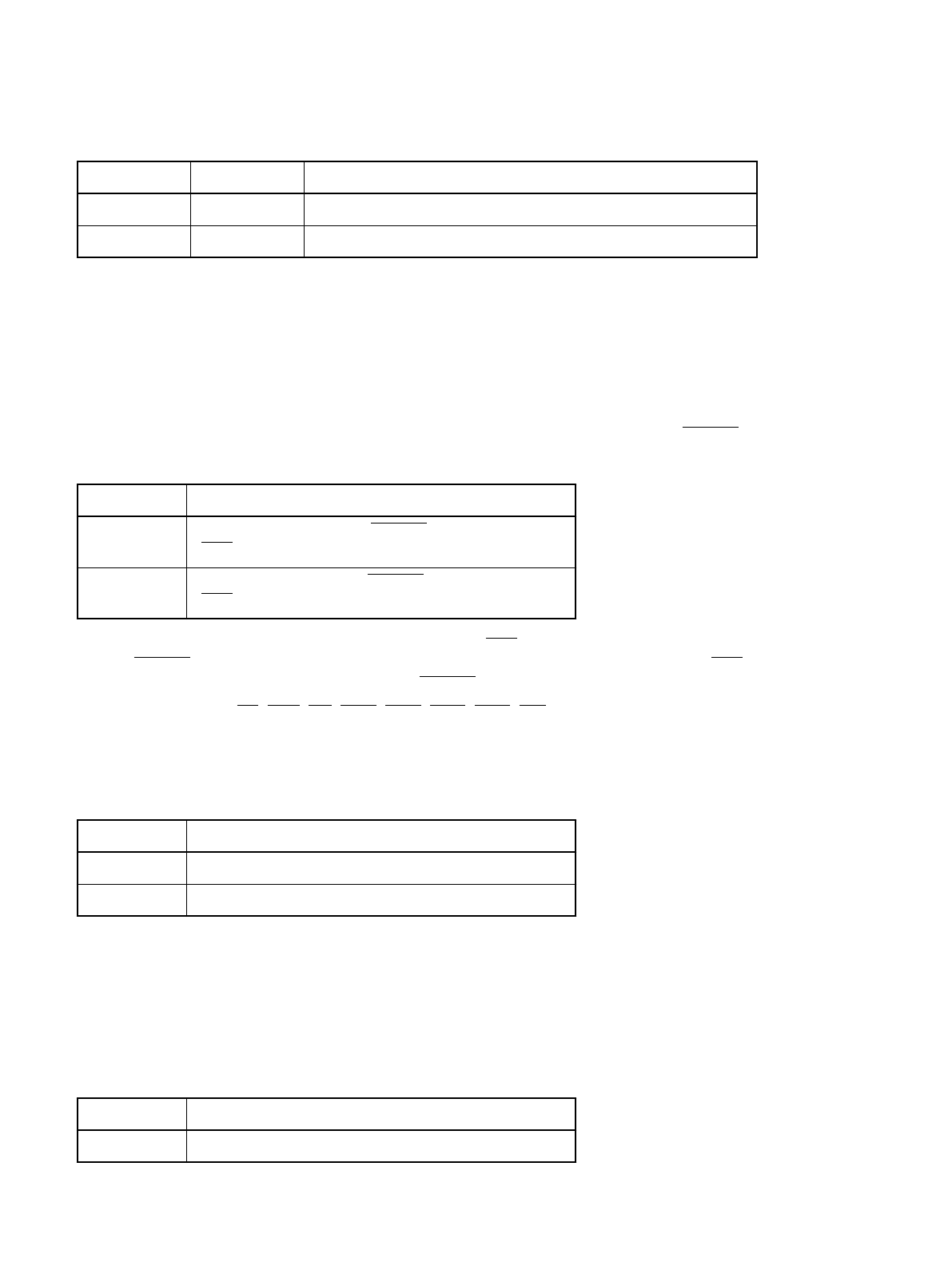

1 0 4 bursts (address boundary: 2 bits)

1 1 8 bursts (address boundary: 3 bits)

SREN Sharing enable/disable

0

Disable sharing by BRQ/BGRNT

(CSn cannot be high impedance)

1

Enable sharing by BRQ/BGRNT

(CSn can be high impedance)

PFEN Prefetch enable/disable

0 Disable prefetch

1 Enable prefetch

WREN Write enable/disable

0 Disable write

Table 2-3 Setting of the Maximum Burst Length of Each Chip Select

BST1 BST0 Maximum burst length