223

Chapter 16 Clock Supervisor

2.Clock Supervisor Register

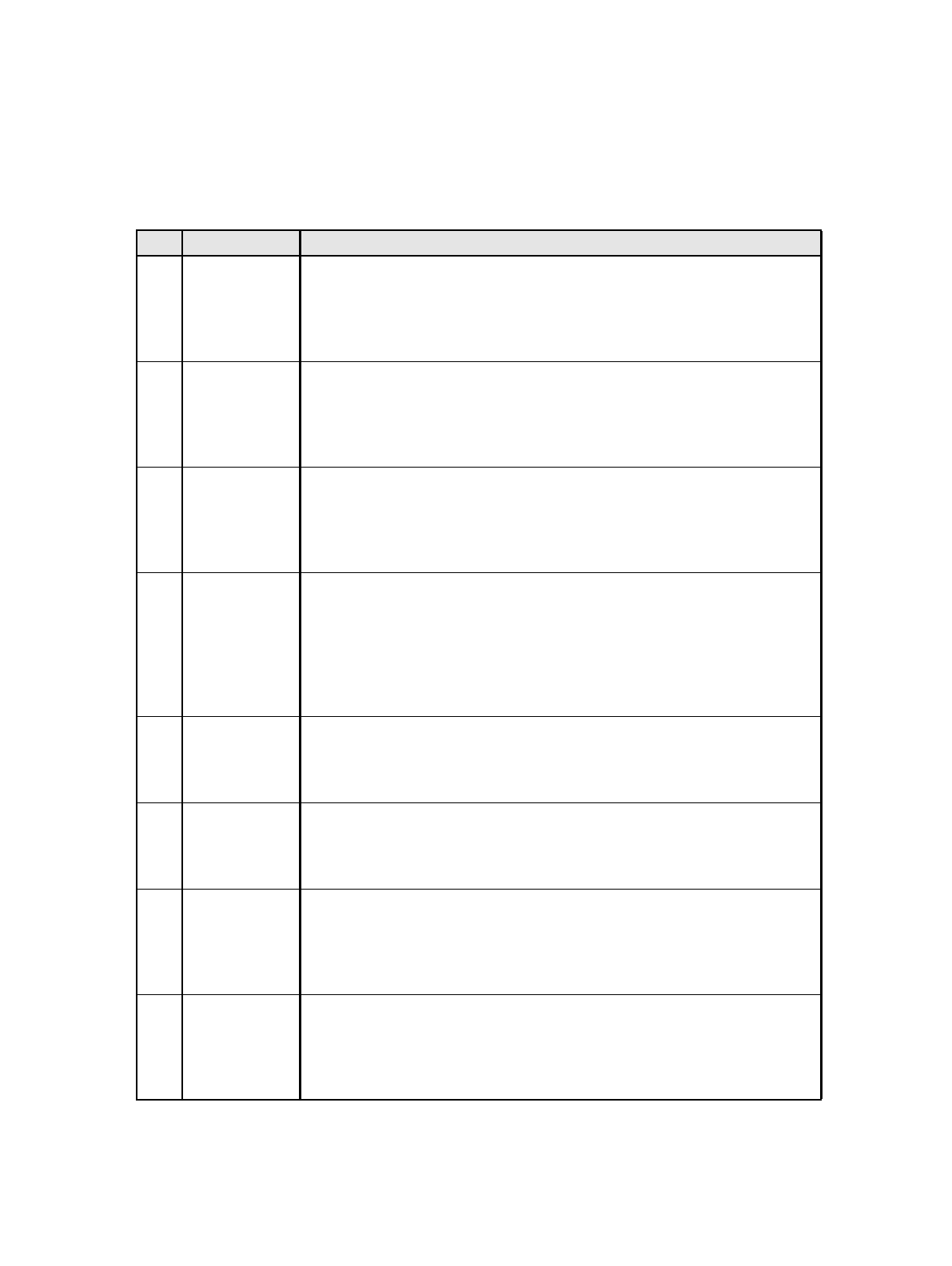

Table 2-1 describes the function of each bit of the Clock Supervisor Control Register (CSVCR).

Table 2-1 Functional Description of each bit of the Clock Supervisor Control Register

Bit Name Function

7 SCKS

(Sub-clock

select)

This bit is to select between 32k external oscillation and internal RC

oscillation as subclock. If this bit is 0 then the external 32k oscillation is

used as subclock, if it’s 1 then the internal RC oscillation is used as

subclock.This bit is cleared to ’0’ by Power-On reset or external reset.

Other types of reset will not affect this bit.

6MM

(Main clock

missing)

If this bit is 1, the main clock supervisor has detected that the main

oscillation clock coming from X0, X1 is missing, e.g. by a broken

crystal. If this bit is 0, a missing main clock has not been detected.

Writing this bit has no effect. This bit is cleared to ’0’ by Power-On reset

or external reset. Other types of reset will not affect this bit.

5SM

(Sub-clock

missing)

If this bit is 1, the sub-clock supervisor has detected that the sub

oscillation clock coming from X0A, X1A is missing, e.g. by a broken

crystal. If this bit is 0, a missing sub-clock has not been detected.

Writing this bit has no effect. This bit is cleared to ’0’ by Power-On reset

or external reset. Other types of reset will not affect this bit.

4 RCE

(RC-oscillator

enable)

Setting this bit to 1 enables the RC-oscillator. Do not disable the RC-

oscillator by setting this bit to 0 while the main or sub-clock supervisors

are still enabled. First the supervisors must be disabled, then it must be

checked that MM and SM are ’0’, then RCE can be set to ’0’. If either

MM or SM bits are ’1’, RCE must not be set to ’0’. This bit is set to ’1’ by

Power-On reset or external reset. Other types of reset will not affect this

bit.

3 MSVE

(Main clock

supervisor

enable)

Setting this bit to 1 enables the main clock supervisor. When this bit is

set to 1, the RC-oscillator must have been enabled by the RCE bit for at

least 100µs. This bit is set to ’1’ by Power-On reset only. Other types of

reset will not affect this bit.

2 SSVE

(Sub-clock

supervisor

enable)

Setting this bit to 1 enables the sub-clock supervisor. When this bit is

set to 1, the RC-oscillator must have been enabled by the RCE bit for at

least 100µs. This bit is set to ’1’ by Power-On reset only. Other types of

reset will not affect this bit.

1 SRST

(Sub-clock

mode reset)

If this bit is set to 1, a reset is performed upon transition from main/PLL

clock mode to sub-clock mode if the sub-clock is already missing. If this

bit is set to 0, no reset is performed in this case. This bit is cleared to ’0’

by Power-On reset or external reset. Other types of reset will not affect

this bit.

0 OUTE

(Output

enable)

This bit can be used as an output enable to output the signals MM (bit 3

of CSVCR) and SM (bit 4 of CSVCR) to port pins. If this bit is set to ’1’,

the ports are enabled for MM and SM output. This bit is cleared to ’0’ by

Power-On reset or external reset. Other types of reset will not affect this

bit.