522

Chapter 31 External Bus

2.External Bus Interface Registers

[Bits 15-12] W15-12 (First Wait Cycle)

These bits set the number of auto-wait cycles to be inserted into the first access cycle of each cycle. Except

for the burst access cycles, only this wait setting is used.

Table 2-5 "Settings for the Number of Auto-Wait Cycles (During First Access)" lists the settings for the number

of auto-wait cycles during first access.

[Bits 11-8] W11-08 (Inpage Access Wait Cycle)

These bits set the number of auto-wait cycles to be inserted into the inpage access cycle during burst access.

They are valid only for burst cycles.

Table 2-6 "Settings for the Number of Auto-Wait Cycles (During Burst Access)" lists the settings for the

number of auto-wait cycles during burst access.

If the same value is set for the first access wait cycle and inpage access wait cycle, the access time for the

address in each access cycle is not the same. This is because the inpage access cycle contains an address

output delay.

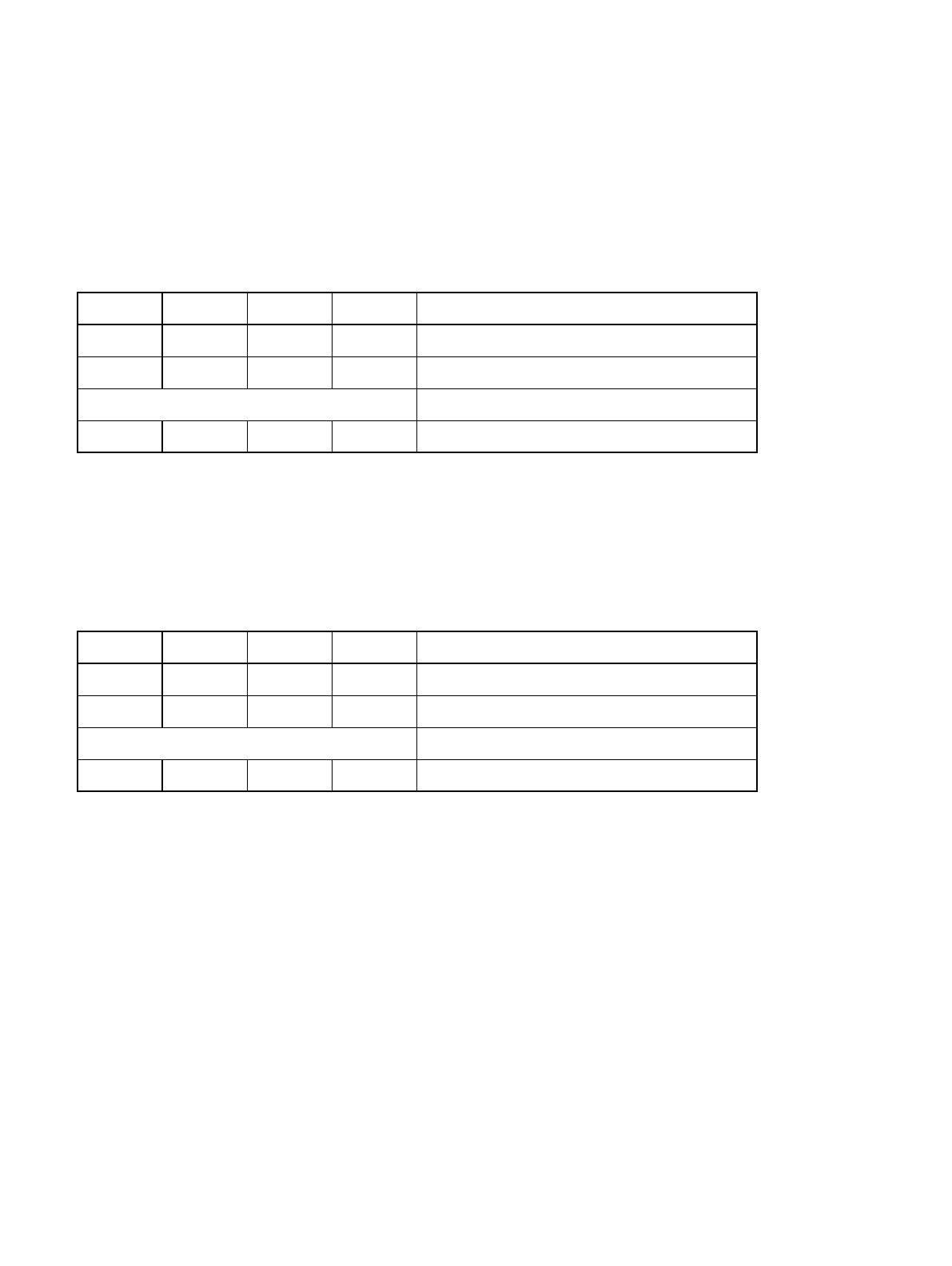

Table 2-5 Settings for the Number of Auto-Wait Cycles (During First Access)

W15 W14 W13 W12 First access wait cycle

0 0 0 0 Auto-wait cycle 0

0 0 0 1 Auto-wait cycle 1

... ...

1 1 1 1 Auto-wait cycle 15

Table 2-6 Settings for the Number of Auto-Wait Cycles (During Burst Access)

W11 W10 W09 W08 Inpage access wait cycle

0 0 0 0 Auto-wait cycle 0

0 0 0 1 Auto-wait cycle 1

... ...

1 1 1 1 Auto-wait cycle 15