198

Chapter 13 Clock Control

4.Registers

4.5 OSCCR: Oscillation Control Register

This register controls the main clock oscillation in subclock mode

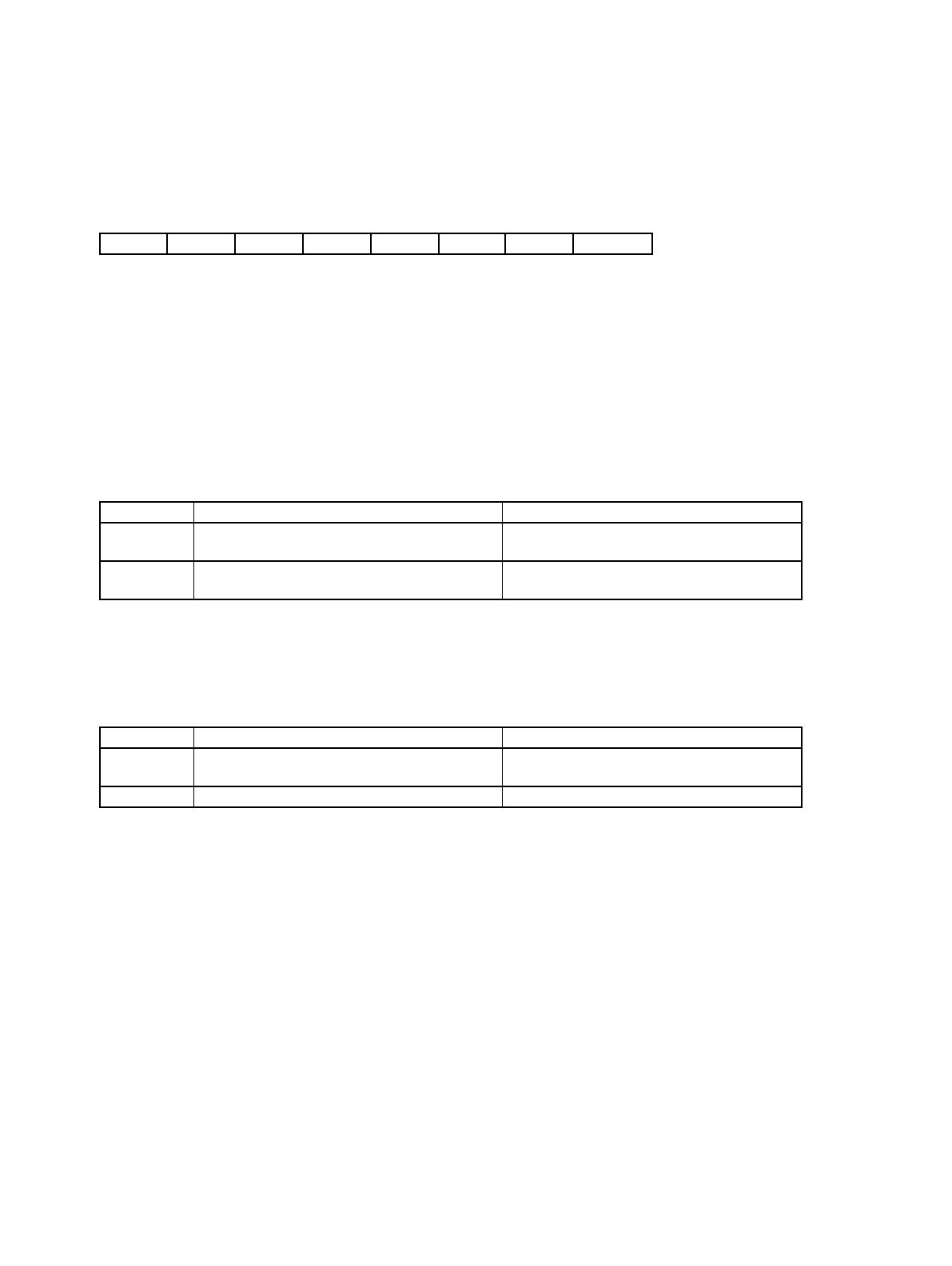

• OSCCR: Address 04CCh (Access: Byte)

(See “Meaning of Bit Attribute Symbols (Page No.10)” for details of the attributes.)

• bit7-2: Undefined bit

Writing does not affect the operation. The read value is undefined.

• bit1: Halt sub clock oscillation in subclock on RC oscillation mode bit

• When the sub clock is selected (CSVCR.SCKS=’0’), specifying the sub clock to halt during subclock

mode (OSCDS2=“1”) is prohibited.

(See “8. Caution (Page No.205)”.)

• bit0: Halt main clock oscillation in subclock mode bit

• When the main clock is selected (CLKS[1:0]=“00”, “01”, “10”), specifying the main clock to halt during

subclock mode (OSCDS1=“1”) is prohibited.

(See “8. Caution (Page No.205)”.)

7 6 5 4 3 2 1 0 bit

– – – – – – OSCDS2 OSCDS1

XXXX0 0 0 0

Initial value (INIT pin

input, watchdog reset)

XXXXXXX X

Initial value

(software reset)

RX/WX RX/WX RX/WX RX/WX RX/WX RX/WX R/W R/W Attribute

OSCDS2 Operation when written to Read value meaning

0

Does not halt sub clock during subclock on RC

oscillation mode.

Sub clock mode can be selected after the

oscillation stabilization time elapses.

1

Halt sub clock during subclock on RC oscillation

mode.

Selecting sub clock mode is prohibited.

OSCDS1 Operation when written to Read value meaning

0 Does not halt main clock during subclock mode.

Main clock mode can be selected after the

oscillation stabilization time elapses.

1 Halt main clock during subclock mode. Selecting main clock mode is prohibited.