627

Chapter 32 USART (LIN / FIFO)

4.USART Registers

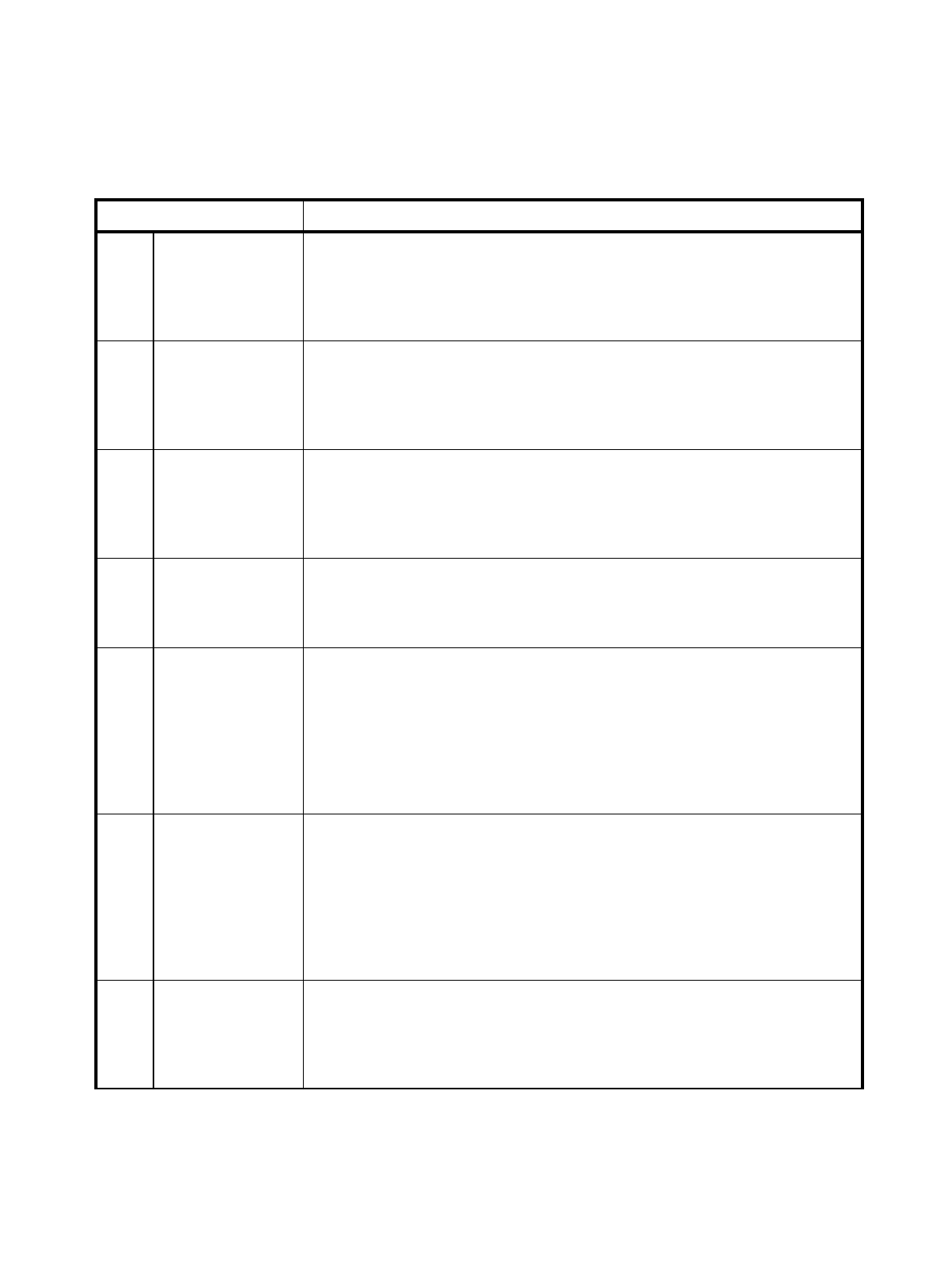

Table 4-5 Functions of each bit of status register 04 (SSR04)

Bit name Function

bit15 PE: Parity error

flag bit

• This bit is set to 1 when a parity error occurs during reception and is

cleared when 0 is written to the CRE bit of the serial control register

(SCR04).

• A reception interrupt request is output when this bit and the RIE bit are 1.

• Data in the reception data register (RDR04) is invalid when this flag is set.

bit14 ORE: Overrun

error flag bit

• This bit is set to 1 when an overrun error occurs during reception and is

cleared when 0 is written to the CRE bit of the serial control register

(SCR04).

• A reception interrupt request is output when this bit and the RIE bit are 1.

• Data in the reception data register (RDR04) is invalid when this flag is set.

bit13 FRE: Framing

error flag bit

• This bit is set to 1 when a framing error occurs during reception and is

cleared when 0 is written to the CRE bit of the serial control register 1

(SCR04).

• A reception interrupt request is output when this bit and the RIE bit are 1.

• Data in the reception data register (RDR04) is invalid when this flag is set.

bit12 RDRF: Receive

data full flag bit

• This flag indicates the status of the reception data register (RDR04).

• This bit is set to 1 when reception data is loaded into RDR04 and can only

be cleared to 0 when the reception data register (RDR04) is read.

• A reception interrupt request is output when this bit and the RIE bit are 1.

bit11 TDRE:

Transmission

data empty flag

bit

• This flag indicates the status of the transmission data register (TDR04).

• This bit is cleared to 0 when transmission data is written to TDR04 and is

set to 1 when data is loaded into the transmission shift register and

transmission starts.

• A transmission interrupt request is generated if this bit and the RIE bit are

1.

<Caution>

This bit is set to 1 (TDR04 empty) as its initial value.

bit10 BDS: Transfer

direction selection

bit

• This bit selects whether to transfer serial data from the least significant bit

(LSB first, BDS=0) or the most significant bit (MSB first, BDS=1).

<Caution>

The high-order and low-order sides of serial data are interchanged with

each other during reading from or writing to the serial data register. If this

bit is set to another value after the data is written to the RDR04 register,

the data becomes invalid.

This bit is fixed to 0 in mode 3 (LIN)

bit9 RIE: Reception

interrupt request

enable bit

• This bit enables or disables input of a request for transmission interrupt to

the CPU.

• A reception interrupt request is output when this bit and the reception data

flag bit (RDRF) are 1 or this bit and one or more error flag bits (PE, ORE,

and FRE) are 1.