312

Chapter 24 Interrupt Control

3.Configuration

3. Configuration

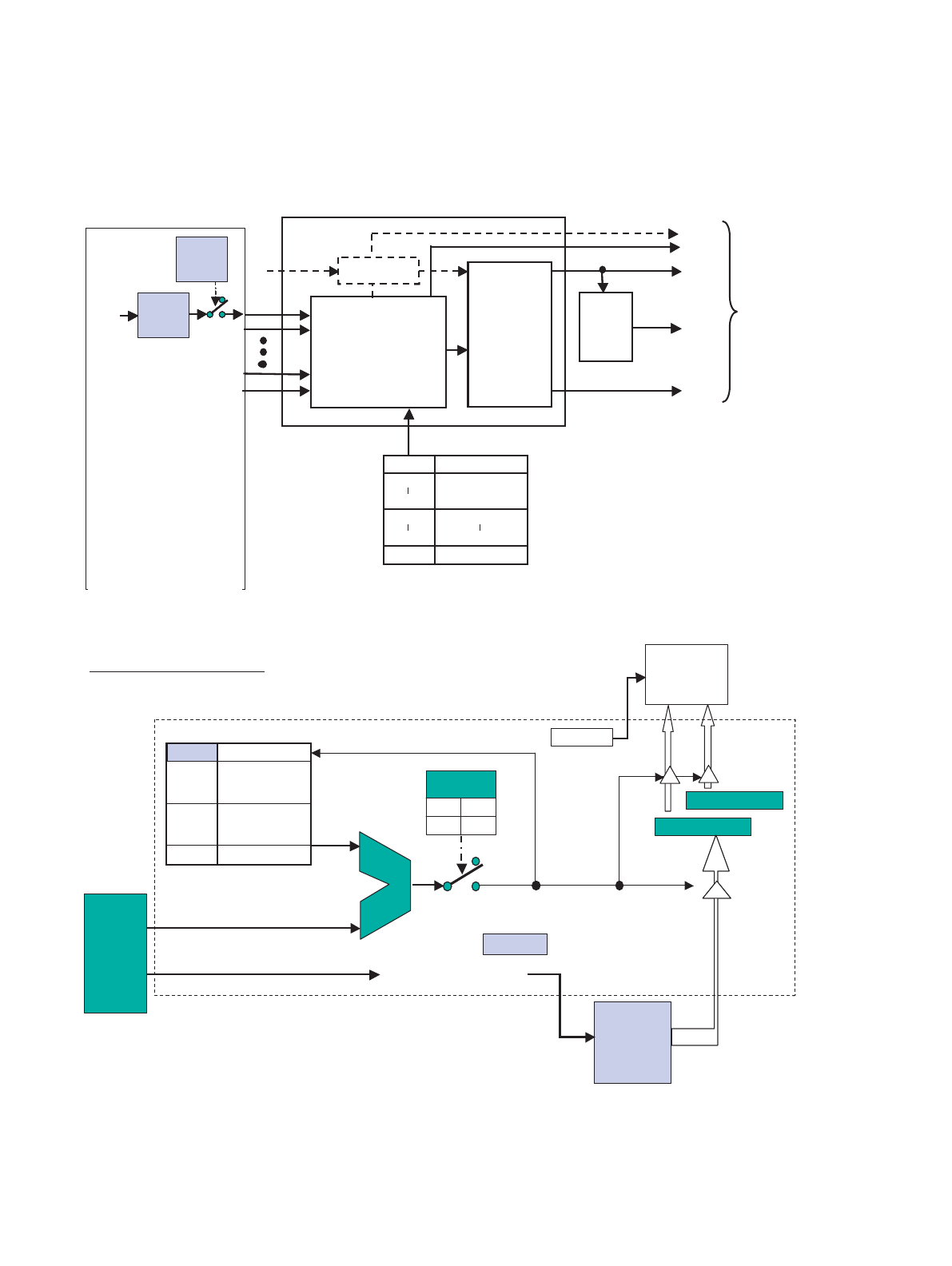

Figure 3-1 Configuration Diagram

Figure 3-2 Configuration Diagram

Interrupt priority

judging circuit

The enabled interrupt request

Interrupt level

/interrupt

number

generator

Wakeup

NMI processing

NMI

Level

Number

HLDREQ

cancel

request

HALT

Priority judging circuit

To the CPU

Interrupt control register

ICR (4-0) ICR0-ICR47: bit4-0

00000

01111

10000

11110

Cannot be set.

Higher interrupt

Lower interrupt

11111

Disable interrupts

External interrupt ( 16)

Reload timer ( 4)

UART receive ( 4)

UART transmit ( 4)

A/D ( 2)

Real-time clock ( 1)

Main clock oscillation

stabilization timer ( 1)

Clock timer ( 1)

Up/down counter ( 2)

PPG ( 3)

Free-run Timer ( 2)

Input capture ( 2)

Output compare ( 4)

Delayed interrupt ( 1)

Reserved for system [REALOS] ( 2)

INT instruction ( 176)

Interrupt

cause

Interrupt

request

flag

Interrupt

request

enable bit

Timebase timer ( 1)

-0)

SSP

(

-0)

(

Interrupt control (CPU side)

Interrupt level [ICRxx: ICR (4-0)]

Interrupt number (#)

Prioritization

Interrupt level mask register

ILM (4-0) ILM register in CPU

00000

l

l

01111

10000

11110

System processing

Interrupt processing

Initial level11111

TBR

Vector table

(1k Bytes)

Initial value: FFC00

Table base register

Interrupt

control

circuit

I flag

0

Disable

1

Enable

SSP

Interrupt number (#) x 4 + TBR

RAM

PC

PS

PS, PC)

The inside of the CPU

Address

Rewrite