402

Chapter 29 MPU / EDSU

3.Break Functions

In Operand address break mode the Operand Address, causing the break is captured in the BOAC register. Addi-

tional BIAC holds the instruction address of the instruction, which was executed one cycle before the break causing

data operation. This is normally the instruction, which has caused the data transfer.

In the operand address break mode the following important points have to be considered:

1) In the FR family architecture, if data access is performed with misalignment, the lower address bit 0 will be ig-

nored for halfword and the lower address bits 0 and 1 for word access. The mask register could be programmed

accordingly.

2) The EDSU operand break does not always occur immediately after completion of execution of the instruction

causing the break event.

3) Please see also information at chapter 3.4 Using operand with data break

3.3 Data value break

The data value break causes a break if specified data is read or written at a data access to an address specified by

the CPU. The data can be specified by the the data value break registers BAD0 and BAD1. Setting the CTC[1:0]

bits of the control register BCR0 to ’11’ provides this mode. The bits EP0 and EP1 in BCR0 enable the break con-

dition.

Up to 2 break points from channels 0 to 1 can be set. All data value break events are ORed into a operand break

exception to the CPU.

1 mask register (BAD0) is available for masking the data value (stored in BAD1) and 1 mask register (BAD2) is avail-

able for masking the operand address (BAD3) which is being accessed. Mask registers BAD2 and BAD0 can be

enabled with EM1 and EM0.

The data on which a break should be executed must be masked by a data-mask on the bus, requiring 32-bit setting

considering the address and data length (see table below). This is required due to the byte position of the operand

is dependent from the operand address. The setting of data length of the control register BCR0 OBS[1:0] could be

configured to all ignored. The data length is controllable by mask setting to the BAD0 register implicitely.

On break at BAD[1:0] the respective flags BD[1:0] in the break interrupt request register BIRQ will be set to ’1’. They

have to be reset by software in the operand break exception routine.

In Operand data value break mode the Operand Address, causing the break is captured in the BOAC register. Ad-

ditional BIAC holds the instruction address of the instruction, which was executed one cycle before the break caus-

ing data operation. This is normally the instruction, which has caused the data transfer.

In the data value break mode the following important points have to be considered:

1) The data value break is also executed for matching DMA transfers. This could lead to unexpected behaviour due

to parallel processes. The filter bits FDMA and FCPU could be set for dedicated investigations.

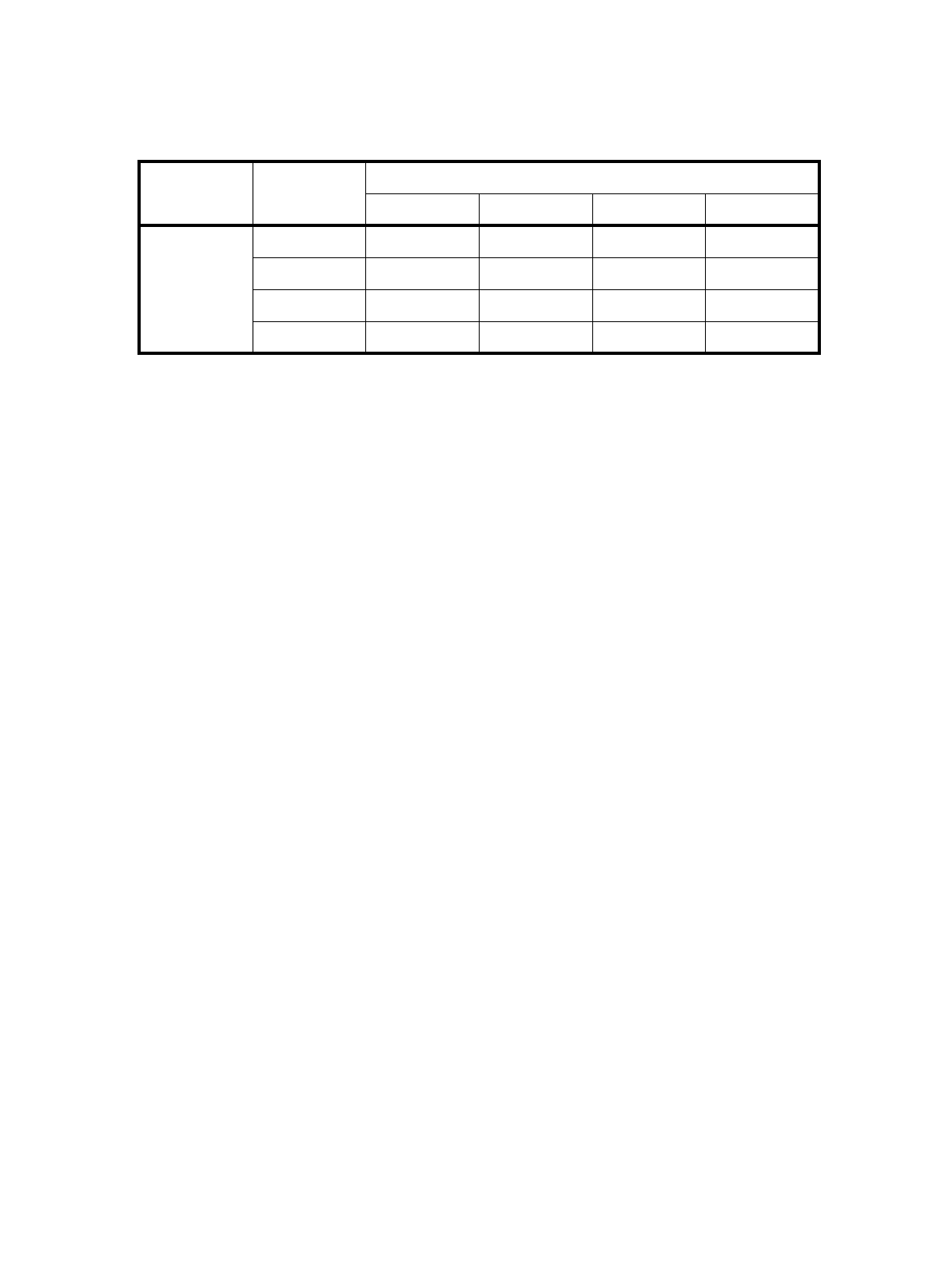

32 bit

4n + 0 Hit Hit Hit Hit

4n + 1 Hit Hit Hit Hit

4n + 2 Hit Hit Hit Hit

4n + 3 Hit Hit Hit Hit

Table 3-3 Operand size and operand address relations

Access data

length

Access

address

Address set in BOA0, BOA1

4n + 0 4n + 1 4n + 2 4n + 3