359

Chapter 26 DMA Controller

3.DMA Controller (DMAC) Operation

Note:

For a demand transfer, be sure to set an external area address for the transfer source or transfer destination or

both. Since DMA transfer is adjusted to the external bus timing in demand transfer mode, access to external

areas is always needed.

● Demand transfer fly-by transfer

A demand transfer fly-by transfer has the same features as a 2-cycle transfer except that the transfer area can

only be external areas, and the transfer unit is read (memory --> I/O) or write (I/O --> memory) only.

● Step/block transfer 2-cycle transfer

For a step/block transfer (Transfer for each transfer request is performed as many times as the specified block

count), all 32-bit areas can be specified as the transfer source/transfer destination address.

[Step transfer]

If 1 is set as the block size, a step transfer sequence is generated.

The following are some features of a step transfer:

• If a transfer request is received, the transfer request is cleared after one transfer operation and then the

transfer is stopped (The DMA transfer request to the bus controller is canceled).

• Another request occurring during transfer is ignored.

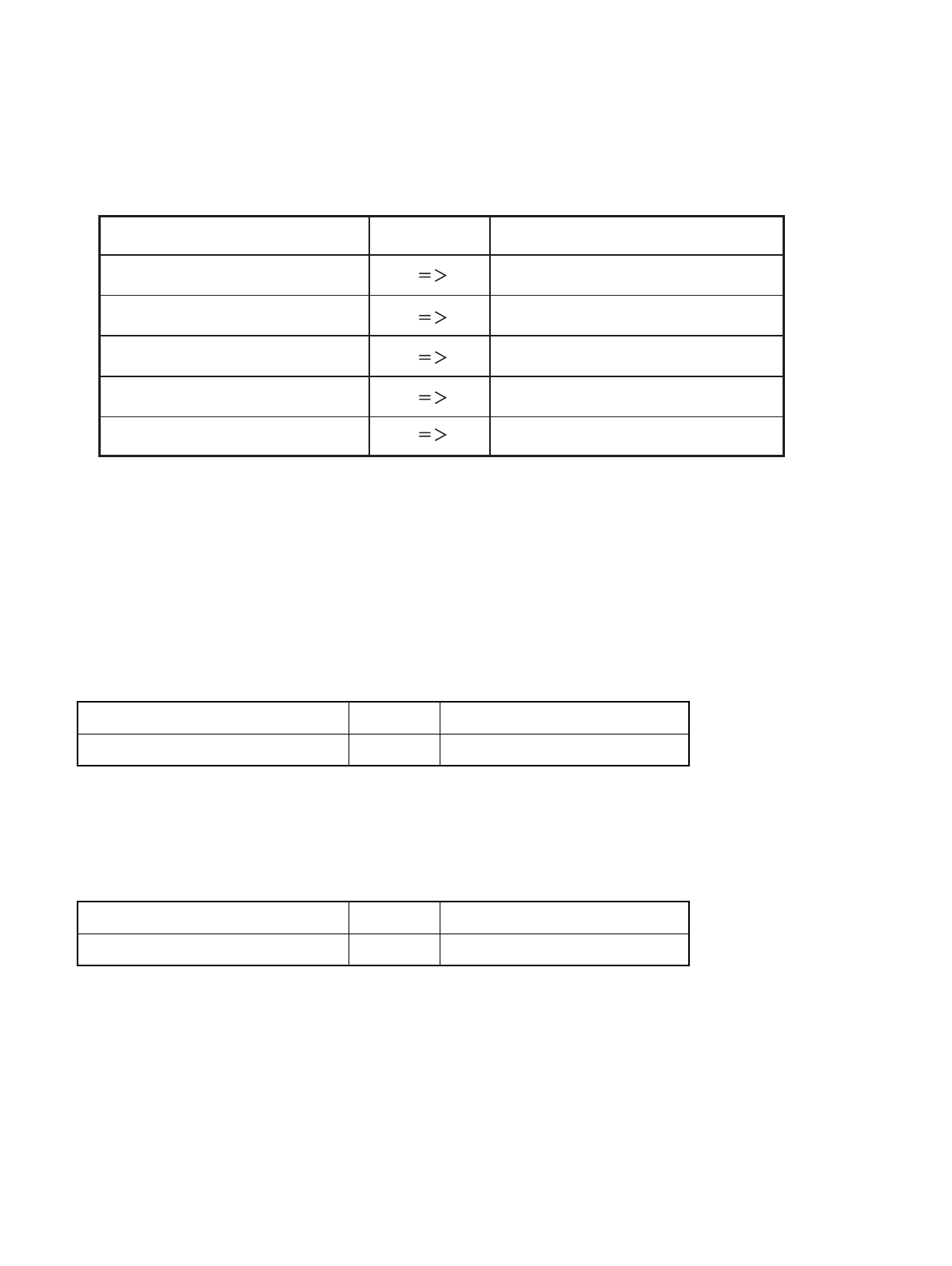

Table 3-3 Specifiable transfer addresses (demand transfer 2-cycle transfer)

Table 3.2-3 Specifiable transfer addresses (demand transfer fly-by transfer)

Transfer source addressing Direction Transfer destination addressing

Specification not required (invalid) => External area

Table 3-4 Specifiable transfer addresses (step/block transfer 2-cycle transfer)

Transfer source addressing Direction Transfer destination addressing

All 32-bit areas specifiable => All 32-bit areas specifiable

Transfer source address Direction Transfer destination addressing

Built-in IO

Built-in RAM

Built-in IO

Built-in RAM

External area

External area

External area External area

External area

External area