716

Chapter 34 CAN Controller

2.Register Description

If more than 32 message buffers are implemented, the following table gives an overview about the additional

flags:

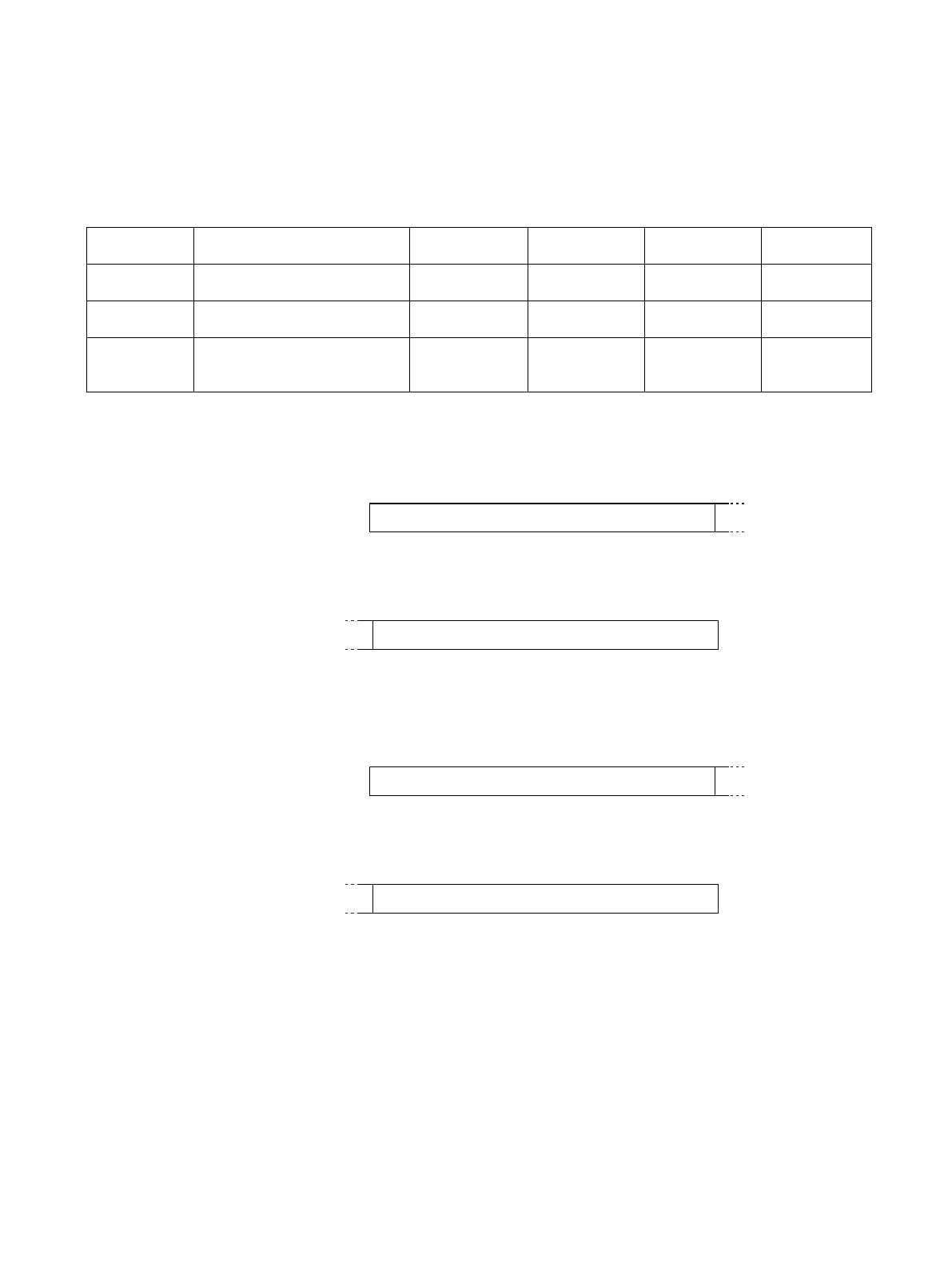

Table 2-1 Additional flags when more than 32 message buffers exist

■ New Data Registers (NEWDT)

addr+0 addr+1 addr+2 addr+3

TREQR 4 & 3 TxRqst 64-33 (address 0x84) TxRqst64-57 TxRqst56-49 TxRqst48-41 TxRqst40-33

TREQR 6 & 5 TxRqst 96-65 (address 0x88) TxRqst96-89 TxRqst88-81 TxRqst80-73 TxRqst72-65

TREQR 8 & 7 TxRqst 128-97 (address 0x8C) TxRqst128-121

TxRqst120-

113

TxRqst112-

105

TxRqst104-97

NewDat32-1 New Data Bits (of all Message Objects)

0

No new data has been written into the data portion of this Message Object by the Message

Handler since last time this flag was cleared by the CPU.

1

The Message Handler or the CPU has written new data into the data portion of this Message

Object.

NewDat32-25

⇐ Bit no.

Read/write ⇒

(R) (R) (R) (R) (R) (R) (R) (R)

Default value⇒

(0) (0) (0) (0) (0) (0) (0) (0)

New Data Register 2 high byte

Address : Base + 0x90

H

15 14 13 12 11 10 9 8

NEWDT2H

NewDat24-17

⇐ Bit no.

Read/write ⇒

(R) (R) (R) (R) (R) (R) (R) (R)

Default value⇒

(0) (0) (0) (0) (0) (0) (0) (0)

Address :

Base + 0x

91H

765432 10

NEWDT2L

New Data Register 2 low byte

NewDat16-9

⇐ Bit no.

Read/write ⇒

(R) (R) (R) (R) (R) (R) (R) (R)

Default value⇒

(0) (0) (0) (0) (0) (0) (0) (0)

New Data Register 1 high byte

Address : Base + 0x92

H

15 14 13 12 11 10 9 8

NEWDT1H

NewDat8-1

⇐ Bit no.

Read/write ⇒

(R) (R) (R) (R) (R) (R) (R) (R)

Default value⇒

(0) (0) (0) (0) (0) (0) (0) (0)

Address :

Base + 0x

93H

765432 10

NEWDT1L

New Data Register 1 low byte