384

Chapter 27 Delayed Interrupt

4.Register

4. Register

4.1 DICR:

Delayed Interrupt Control Register

This register controls to generate/clear the delayed interrupt.

• DICR: Address 0038h (Access: Byte)

(Refer to “Meaning of Bit Attribute Symbols (Page No.10)” for the attributes.)

• Bit7-1: Undefined: Writing does not affect operation. The read value is undefined.

• Bit0: Delayed interrupt control bit

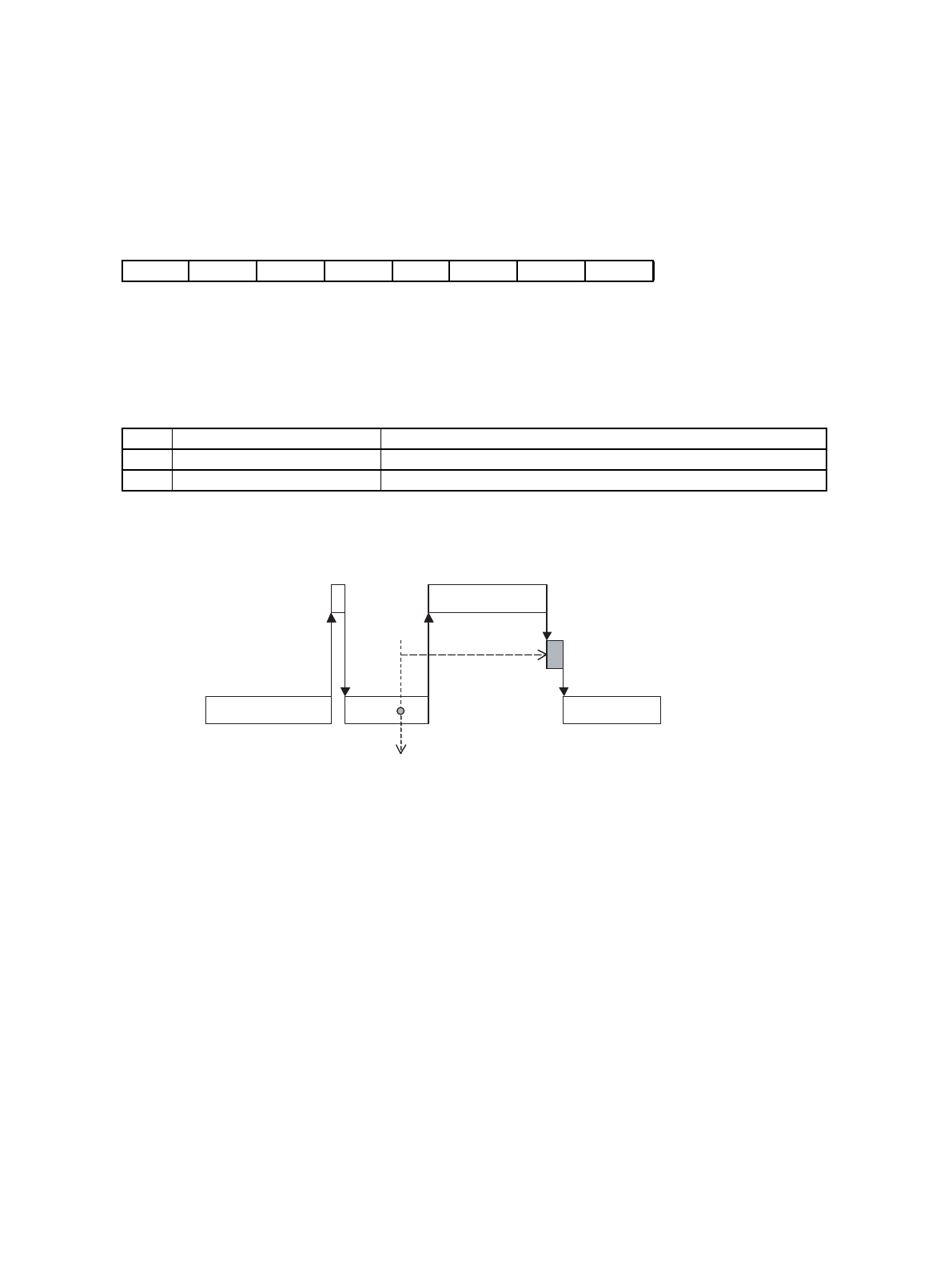

5. Operation

Delayed interrupt service

(1) In OS, a request for task B dispatch is generated

(2) OS sets the delayed interrupt return destination (dispatch destination)

(3) OS sets the delayed interrupt (delayed interrupt generation)

(4) When OS returns, the interrupt with the highest priority sequence takes place, because an interrupt

service is prohibited in OS

(5) When the interrupt with the highest priority is completed, delayed interrupt takes place

(6) In delayed interrupt, delayed interrupt is released

(7) Returned from the delayed interrupt (dispatched to task B)

7 6 5 4 3 2 1 0 bit

–––––––DLYI

– – – – – – – 0 Initial value

RX/WX RX/WX RX/WX RX/WX

RX/

WX

RX/WX RX/WX R/W Attribute

DLYI Read operation Write operation

0 No delayed interrupt request Delayed interrupt request clear

1 Delayed interrupt request Delayed interrupt request generation

Task A

OS

Preference interrupt

Task B

A task dispatch request is generated.

Setting for the dispatch destination (Delay return destination)

Setting for the delay interrupt request (Generating)

Delay interrupt

Delay

(1)

(2)

(3)

(4)

(5)

(7)(6)