626

Chapter 32 USART (LIN / FIFO)

4.USART Registers

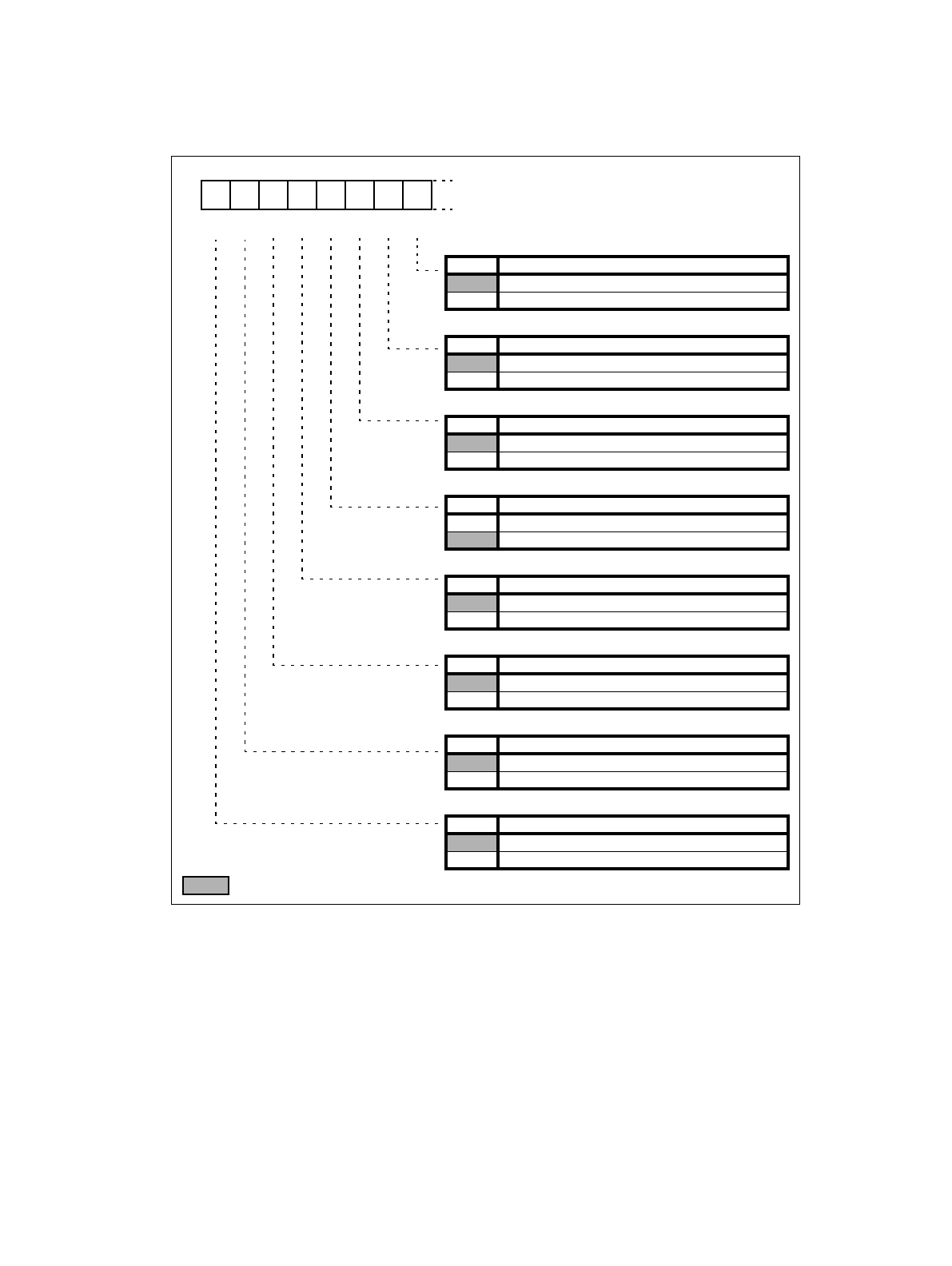

Figure 4-3 Configuration of the Serial Status register 04 (SSR04)

15 14 13 12 11 10 9 8

Initial value

0 0 0 0 1 0 0 0

B

RRRR R/WR R/W R/W

bit8

TIE Transmission Interrupt enable

0 Disables Transmission Interrupt

1 Enables Transmission Interrupt

bit9

RIE Reception Interrupt enable

0 Disables Reception Interrupt

1 Enables Reception Interrupt

bit10

BDS Bit direction setting

0 send / receive LSB first

1 send / receive MSB first

bit11

TDRE Transmission data register empty

0 Transmission data register is full

1 Transmission data register is empty

bit12

RDRF Reception data register full

0 Reception data register is empty

1 Reception data register is full

bit13

FRE Framing error

0 No framing error occurred

1 A framing error occurred during reception

bit14

ORE Overrun error

0 No overrun error occurred

1 An overrun error occurred during reception

bit15

PE Parity error

0 No parity error occurred

1 A parity error occurred during reception

R/W : Readable and writable

R : Flag is read only, writing to it

has no effect

: Initial value