335

Chapter 26 DMA Controller

2.DMA Controller (DMAC) Registers

2. DMA Controller (DMAC) Registers

This section describes the configuration and functions of the registers used by the DMA control-

ler (DMAC).

■ DMA Controller (DMAC) registers

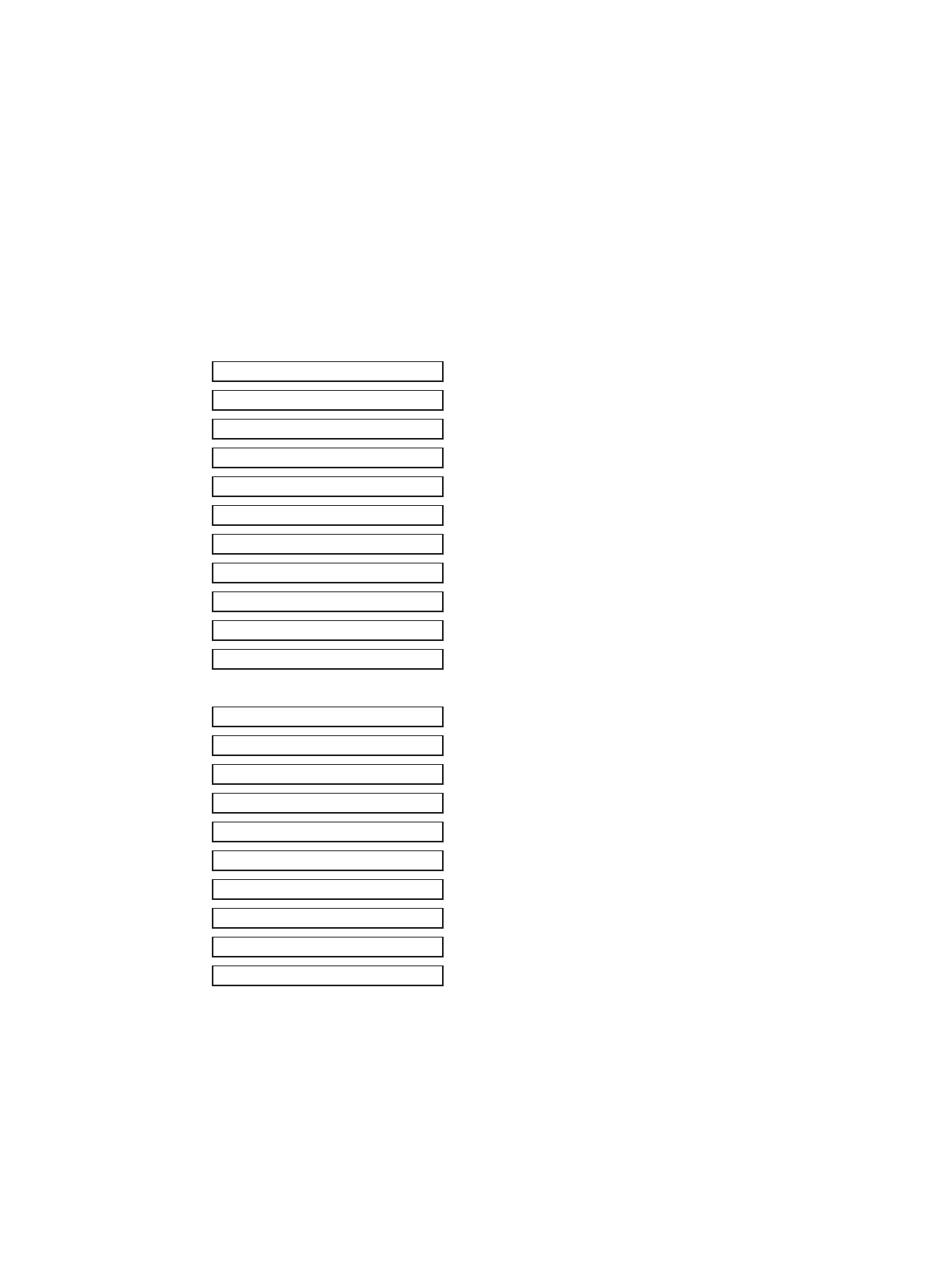

Figure 2-1"DMA Controller (DMAC) Registers" shows the registers of the DMA controller (DMAC).

Figure 2-1 DMA Controller (DMAC) Registers

■ Notes on Setting Registers

When the DMA controller (DMAC) is set, some bits need to be set while DMA is stopped. If they are set while

DMA is in progress (during transfer), correct operation cannot be guaranteed.

An asterisk following a bit when its function is described later indicates that the operation of the bit is affected if it

is set during DMAC transfer. Rewrite this bit while DMAC transfer is stopped (start is disabled or temporarily

stopped).

24 31 23 16 15 08 07 00

ch.0

ch.0

ch.1

ch.1

ch.2

ch.2

ch.3

ch.3

ch.4

ch.4

ch.0

ch.0

ch.1

ch.1

ch.2

ch.2

ch.3

ch.3

ch.4

ch.4

(bit)

Control/status register A

Control/status register B

(DMACA0)

Control/status register A

Control/status register B

(DMACB0)

(DMACA1)

Control/status register A

Control/status register B

Control/status register A

Control/status register B

Control/status register A

Control/status register B

All-channel control register

(DMACB1)

(DMACA2)

(DMACB2)

(DMACA3)

(DMACB3)

(DMACA4)

(DMACB4)

(DMACR)

Transfer source address register (DMASA0)

Transfer destination address register (DMADA0)

Transfer source address register

Ttransfer destination address register

(DMASA1)

(DMADA1)

Transfer source address register (DMASA2)

Transfer destination address register (DMADA2)

Transfer source address register (DMASA3)

Transfer destination address register (DMADA3)

Transfer source address register

Transfer destination address register

(DMASA4)

(DMADA4)