339

Chapter 26 DMA Controller

2.DMA Controller (DMAC) Registers

Notes:

• If DMA start resulting from an interrupt from a peripheral function is set (IS=1xxxx

B

), disable interrupts from

the selected peripheral function with the ICR register.

• If demand transfer mode is selected, only IS[4:0]=01110

B

, 01111

B

can be set. Starting by other sources is

disabled.

• External request input is valid only for CH0, 1, and 2. External request input cannot be selected for CH2, CH3

and 4. Whether level detection or edge detection is used is determined by the mode setting. Level detection is

selected for demand transfer. For all other cases, edge detection is selected.

[Bits 23 to 20] EIS3 to 0 (Extended Input Select)*: Extended Transfer Source Selection

These bits select the source of a transfer request note that the software transfer request by the STRG bit

function is always valid regardless of the setting of these bits. As listed in Table 2-2 "Settings for Extended

Transfer Request Sources".

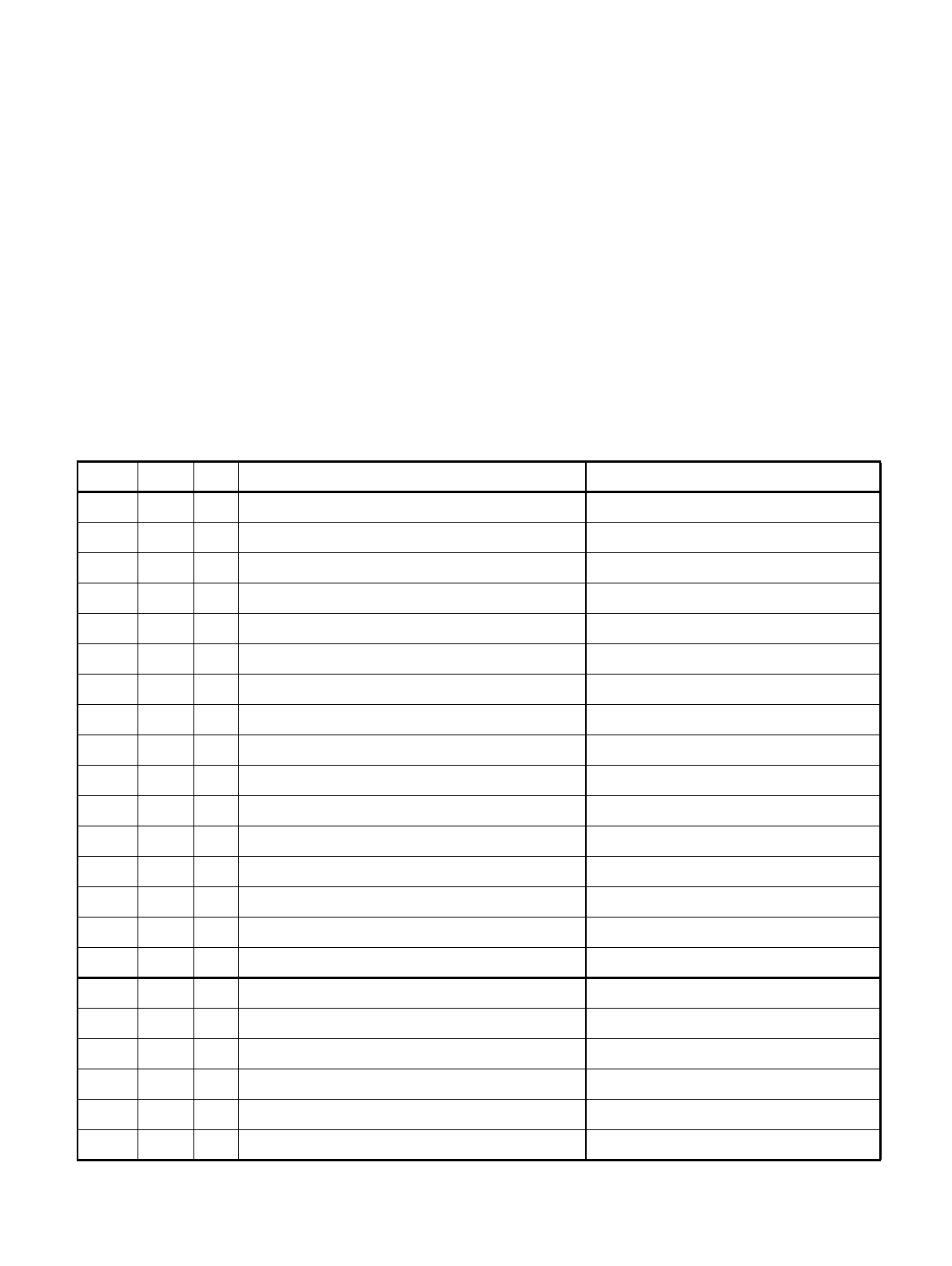

Table 2-2 Settings for Extended Transfer Request Sources

IS EIS RN Function Transfer stop request

10000 0001 16 External Interrupt 0 -

10001 0001 17 External Interrupt 1 -

10010 0001 18 External Interrupt 2 -

10011 0001 19 External Interrupt 3 -

10100 0001 20 External Interrupt 4 -

10101 0001 21 External Interrupt 5 -

10110 0001 22 External Interrupt 6 -

10111 0001 23 External Interrupt 7 -

11000 0001 24 res. -

11001 0001 25 res. -

11010 0001 26 res. -

11011 0001 27 res. -

11100 0001 28 res. -

11101 0001 29 res. -

11110 0001 30 res. -

11111 0001 31 res. -

10000 0010 32 Reload Timer 0 -

10001 0010 33 Reload Timer 1 -

10010 0010 34 Reload Timer 2 -

10011 0010 35 Reload Timer 3 -

10100 0010 36 Reload Timer 4 -

10101 0010 37 Reload Timer 5 -