569

Chapter 31 External Bus

5.Operation of the Ordinary bus interface

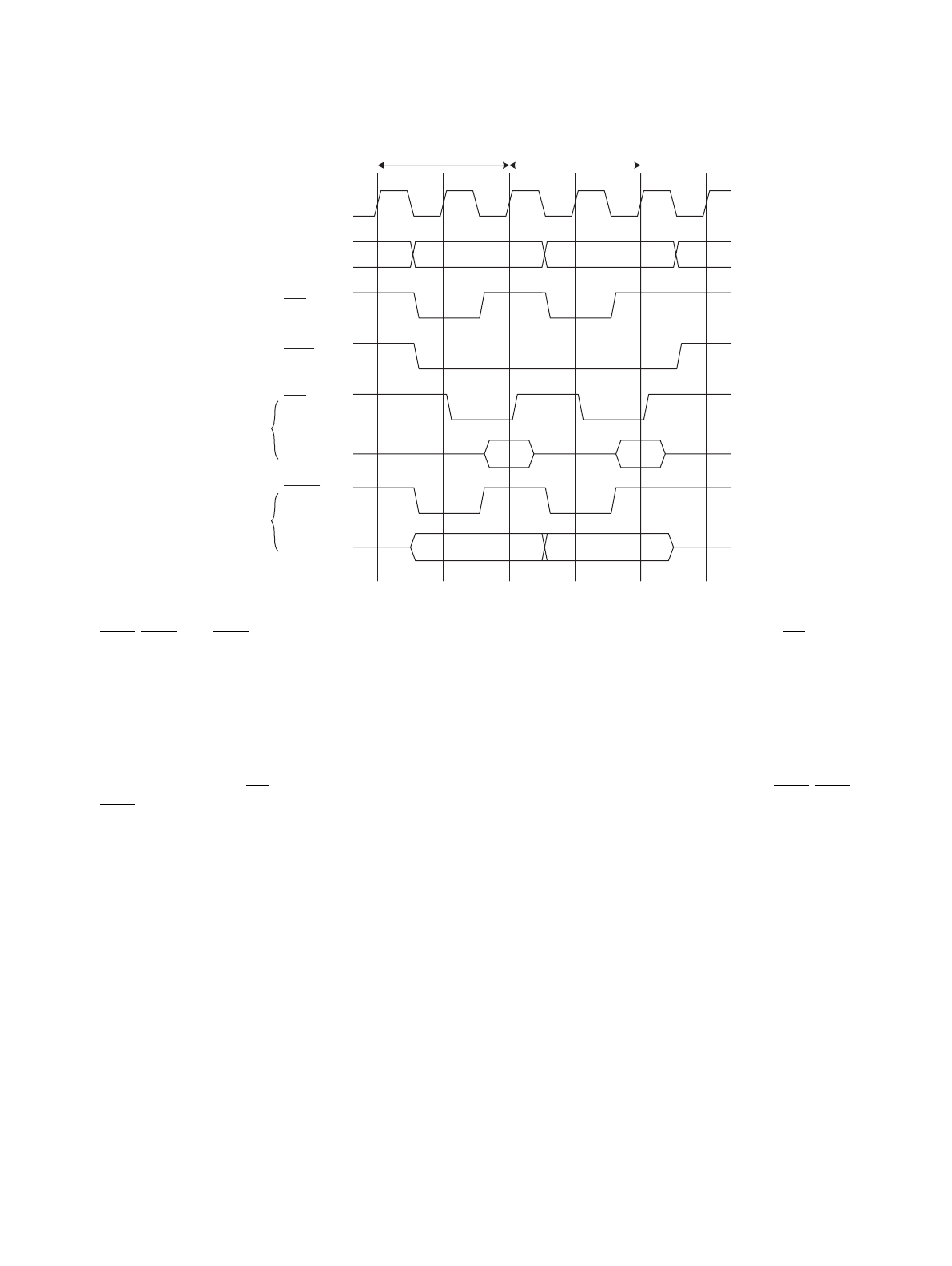

Figure 5-7 Timing Chart for Synchronous Write Enable Output

• If synchronous write enable output is enabled (If the W03 bit of the AWR is 1), operation is as follows.

• WR0-WR3 and WRn pin output asserts synchronous write enable output at the timing at which AS pin output

is asserted. For a write to an external bus, the synchronous write enable output is L. For a read from an

external bus, the synchronous write enable output is H.

• Write data is output from the external data output pin in the clock cycle following the cycle in which

synchronous write enable output is asserted. If write data cannot be output because the internal bus is

temporarily unavailable, assertion of synchronous write enable output may be extended until write data can be

output.

• Read strobe output (RD) functions as an asynchronous read strobe regardless of the setting of WR0-WR3 and

WRn output timing. Use it as is for controlling the data I/O.

Read

Write

#1

#2

#1 #2

#1 #2

MCLK

AS

CSn *

RD

D[31:0]

WRn

D[31:0]

A[31:0]