345

Chapter 26 DMA Controller

2.DMA Controller (DMAC) Registers

[Bits 29, 28] MOD (MODe)*: Transfer mode setting

These bits are the transfer mode setting bits and set the operating mode of the corresponding channel.

• When reset: Initialized to 00

B

.

• These bits are readable and writable.

[Bits 27 to 26] WS (Word Size)*: Transfer data width selection

These bits are the transfer data width selection bits and are used to select the transfer data width of the

corresponding channel. Transfer operations are repeated in units of the data width specified in this register for

as many times as the specified count.

• When reset: Initialized to 00

B

.

• These bits are readable and writable.

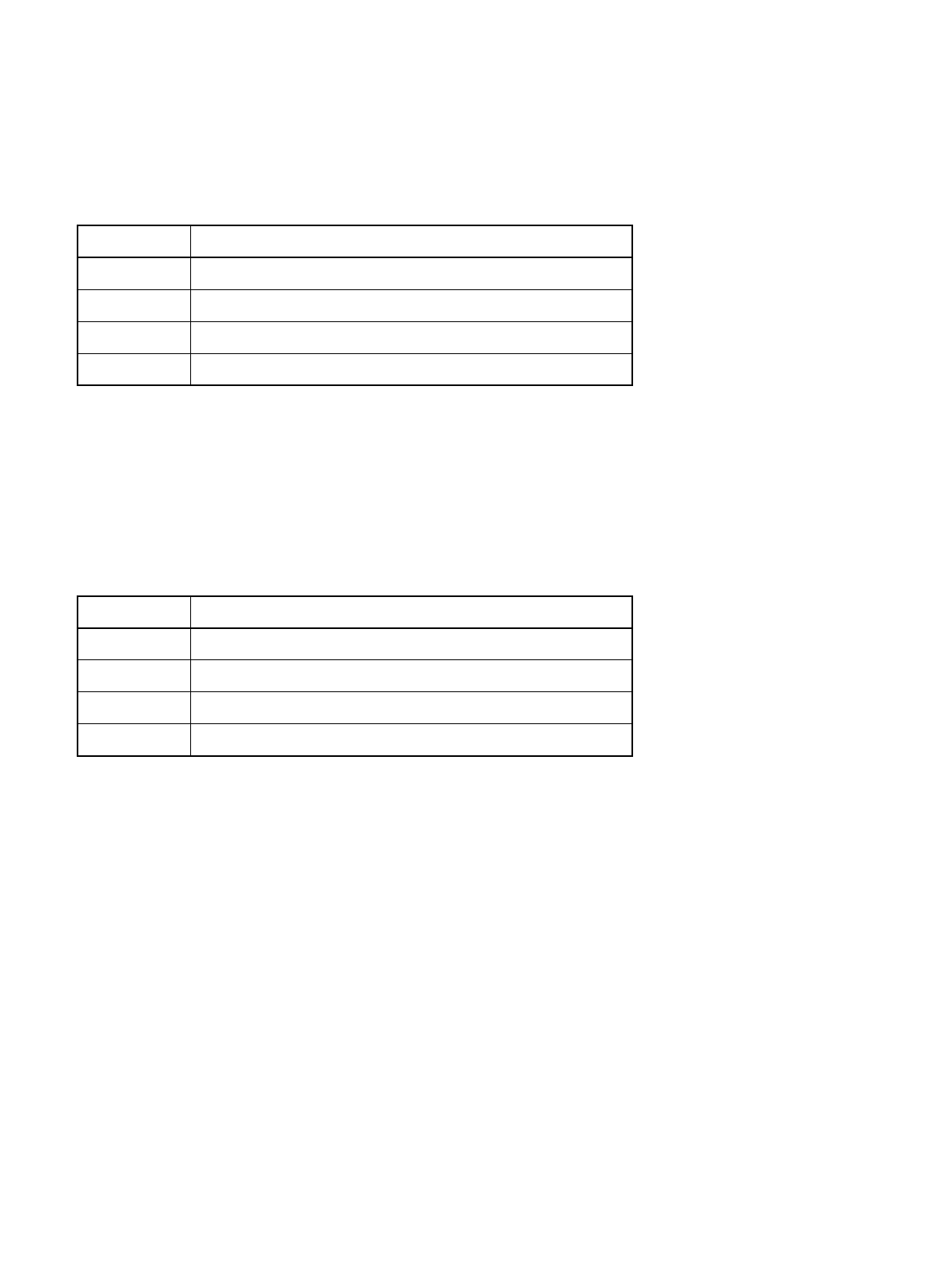

Table 2-4 Settings for Transfer Modes

MOD Function

00

B

Block/step transfer mode (initial value)

01

B

Burst transfer mode

10

B

Demand transfer mode

11

B

Setting disabled

Table 2-5 Selection of the Transfer Data Width

WS Function

00

B

Byte-width transfer (initial value)

01

B

Halfword-width transfer

10

B

Word-width transfer

11

B

Setting disabled