710

Chapter 34 CAN Controller

2.Register Description

■ IFx Message Control Register (IFxMCTR)

■ IFx Data A and Data B Registers (IFxDTA, IFxDTB)

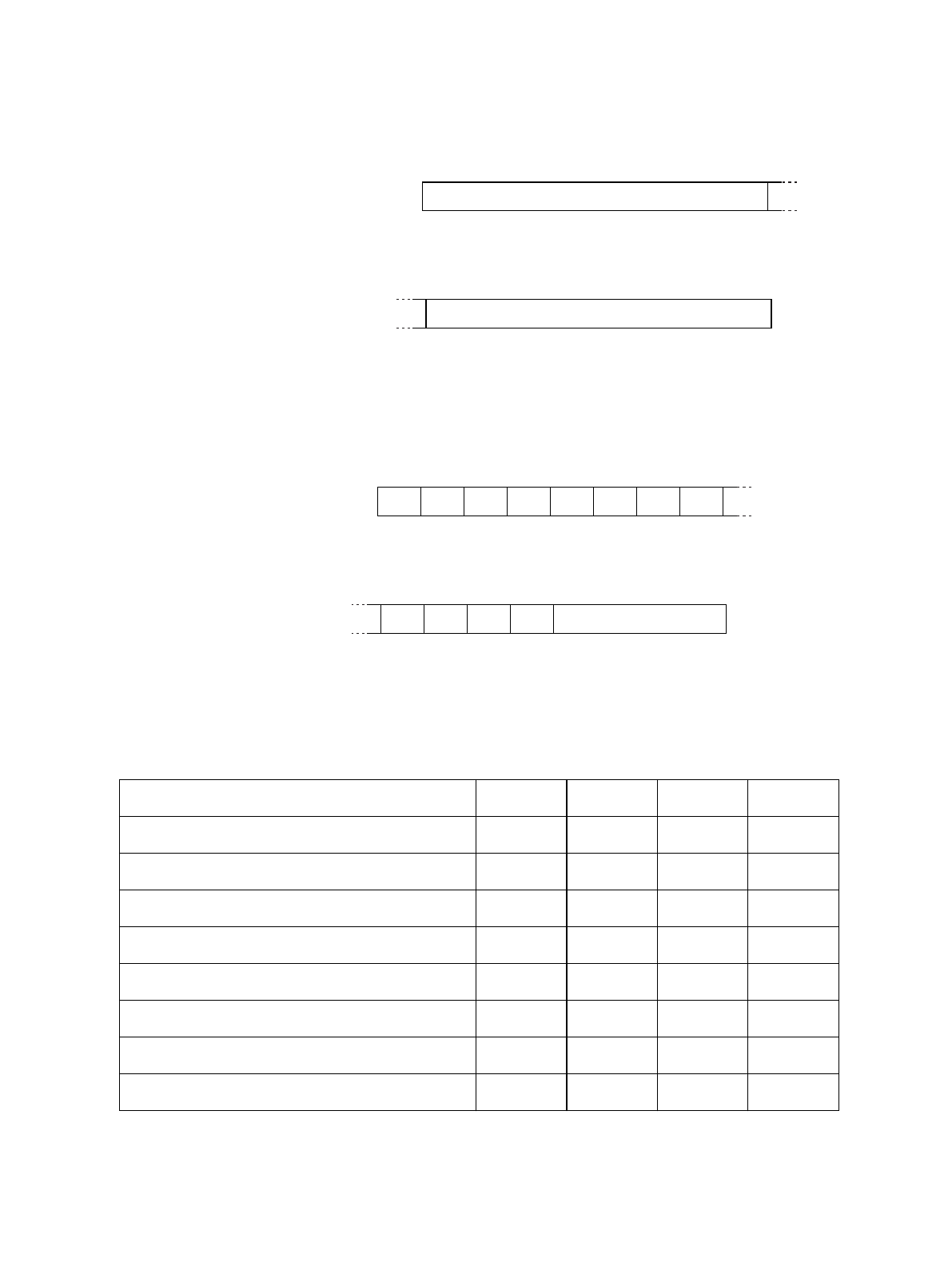

The data bytes of CAN messages are stored in the IFx Message Buffer Registers in the following order:

In a CAN Data Frame, Data(0) is the first, Data(7) is the last byte to be transmitted or received. In CAN’s serial

bit stream, the MSB of each byte will be transmitted first.

addr+0 addr+1 addr+2 addr+3

IFxMessage Data A1 (addresses 0x20 & 0x50) Data(0) Data(1)

IFx Message Data A2 (addresses 0x22 & 0x52) Data(2) Data(3)

IFx Message Data B1 (addresses 0x24 & 0x54) Data(4) Data(5)

IFx Message Data B2 (addresses 0x26 & 0x56) Data(6) Data(7)

IFx Message Data A2 (addresses 0x30 & 0x60) Data(3) Data(2)

IFx Message Data A1 (addresses 0x32 & 0x62) Data(1) Data(0)

IFx Message Data B2 (addresses 0x34 & 0x64) Data(7) Data(6)

IFx Message Data B1 (addresses 0x36 & 0x66) Data(5) Data(4)

ID15-8

⇐ Bit no.

Read/write ⇒

(R/W) (R/W) (R/W) (R/W) (R/W) (R/W) (R/W) (R/W)

Default value⇒

(0) (0) (0) (0) (0) (0) (0) (0)

IFx Arbitration 1 Register high byte

Address : Base + 0x1A

H &

Base + 0x4A

H

15 14 13 12 11 10 9 8

IFxARB1H

ID7-0

⇐ Bit no.

Read/write ⇒

(R/W) (R/W) (R/W) (R/W) (R/W) (R/W) (R/W) (R/W)

Default value⇒

(0) (0) (0) (0) (0) (0) (0) (0)

Address :

Base + 0x

1BH &

Base + 0x

4BH

765432 10

IFxARB1L

IFx Arbitration 1 Register low byte

NewDat MsgLst IntPnd UMask TxIE RxIE RmtEn TxRqst

⇐ Bit no.

Read/write ⇒

(R/W) (R/W) (R/W) (R/W) (R/W) (R/W) (R/W) (R/W)

Default value⇒

(0) (0) (0) (0) (0) (0) (0) (0)

IFx Message Control Register high byte

A

ddress : Base + 0x1C

H &

Base + 0x4C

H

15 14 13 12 11 10 9 8

IFxMCTRH

EoB res res res

DLC3-0

⇐ Bit no.

Read/write ⇒

(R/W) (R) (R) (R) (R/W) (R/W) (R/W) (R/W)

Default value⇒

(0) (0) (0) (0) (0) (0) (0) (0)

Address :

Base + 0x

1DH &

Base + 0x

4DH

765432 10

IFxMCTRL

IFx Message Control Register low byte