843

Chapter 41 Up/Down Counter

4.Register

4.2 UDCS: Count Status Register

This register is used to control Up/Down Counter and to indicate the status of the counter.

• UDCS0 (Up/Down Counter 0): Address 0307

H

(Access: Byte, Half-Word)

• UDCS1 (Up/Down Counter 1): Address 030B

H

(Access: Byte, Half-Word)

• UDCS2 (Up/Down Counter 2): Address 0317

H

(Access: Byte, Half-Word)

• UDCS3 (Up/Down Counter 3): Address 031B

H

(Access: Byte, Half-Word)

(For attributes, refer to “Meaning of Bit Attribute Symbols (Page No.10)”.)

• bit7: Enable count operation

• bit6: Enable compare interrupt requests

Setting the interrupt request permission bit to “1” enables the interrupt request flag (CMPF).

• bit5: Enable overflow/underflow interrupt requests

Setting the interrupt request permission bit to “1” enables the interrupt request flag (OVFF or UDFF).

• bit4: Compare detection flag

To enable interrupt requests, the interrupt request permission bit must be set (CITE= “1”).

• bit3: Overflow detection flag

To enable interrupt requests, the interrupt request permission bit must be set (UDIE= “1”).

• bit2: Underflow detection flag

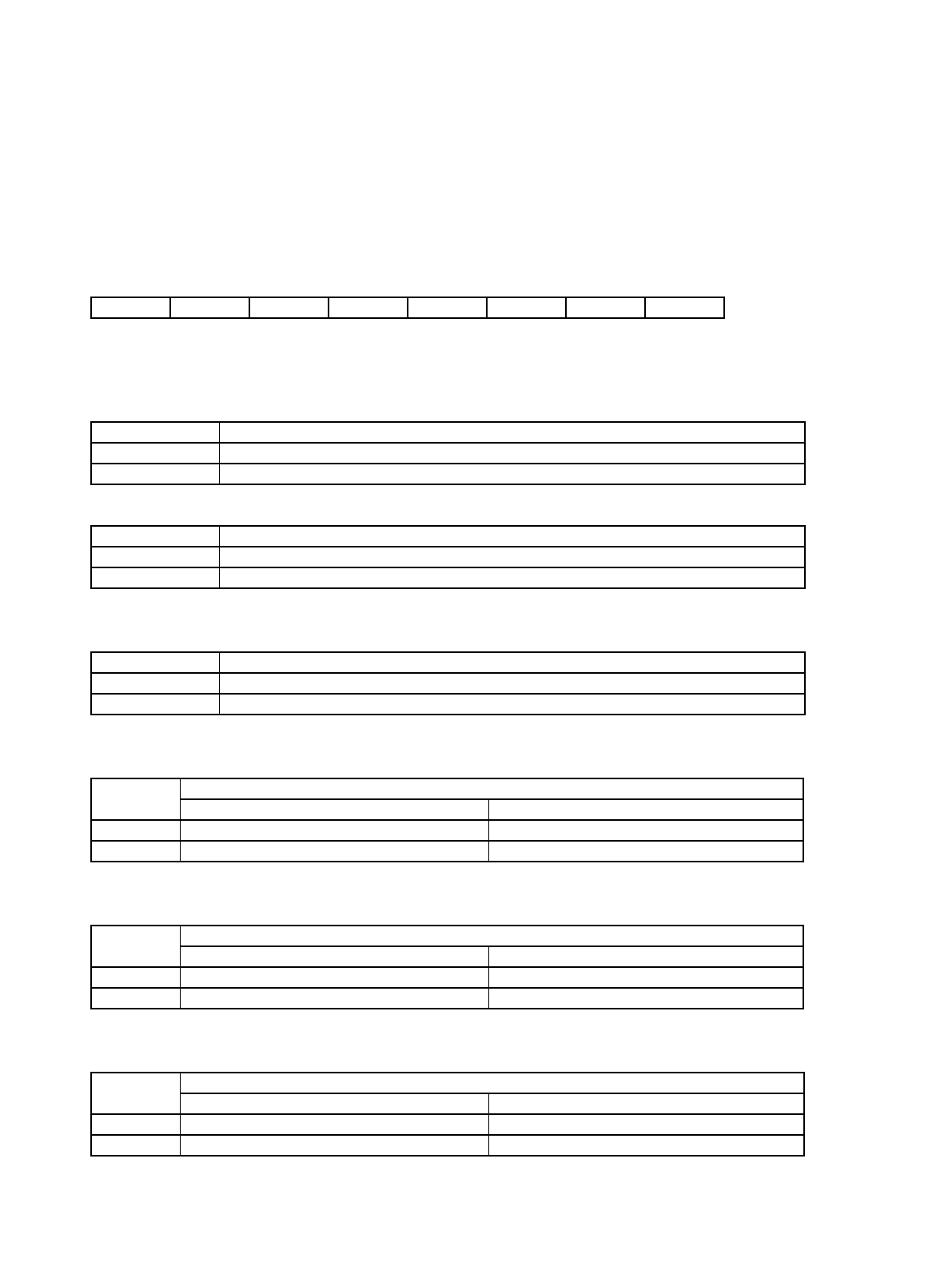

76543210bit

CSTR CITE UDIE CMPF OVFF UDFF UDF1 UDF0

0 0 0 0 0 0 0 0 Initial value

R/W R/W R/W R/W0 R/W0 R/W0 R/WX R/WX Attribute

CSTR Count operation

0 Disable count operation.

1 Enable count operation. (Activate counter.)

CITE Compare interrupt request

0 Disable compare interrupt requests.

1 Enable compare interrupt requests.

UDIE Overflow/underflow interrupt request

0 Disable overflow/underflow interrupt requests.

1 Enable overflow/underflow interrupt requests.

CMPF

Compare detection

When read: When written:

0 Comparison results do not agree. Clear the flag.

1 Comparison results agree. Disable setting.

OVFF

Overflow detection

When read: When written:

0 No overflow Clear the flag.

1 An overflow has occurred. Disable setting.

UDFF

Underflow detection

When read: When written:

0 No Underflow Clear the flag.

1 An underflow has occurred. Disable setting.