140

Chapter 9 Reset

3.Configuration

• A settings initialization reset (INIT) is followed by an operation reset (RST) after the oscillation

stabilization time elapses.

3. Configuration

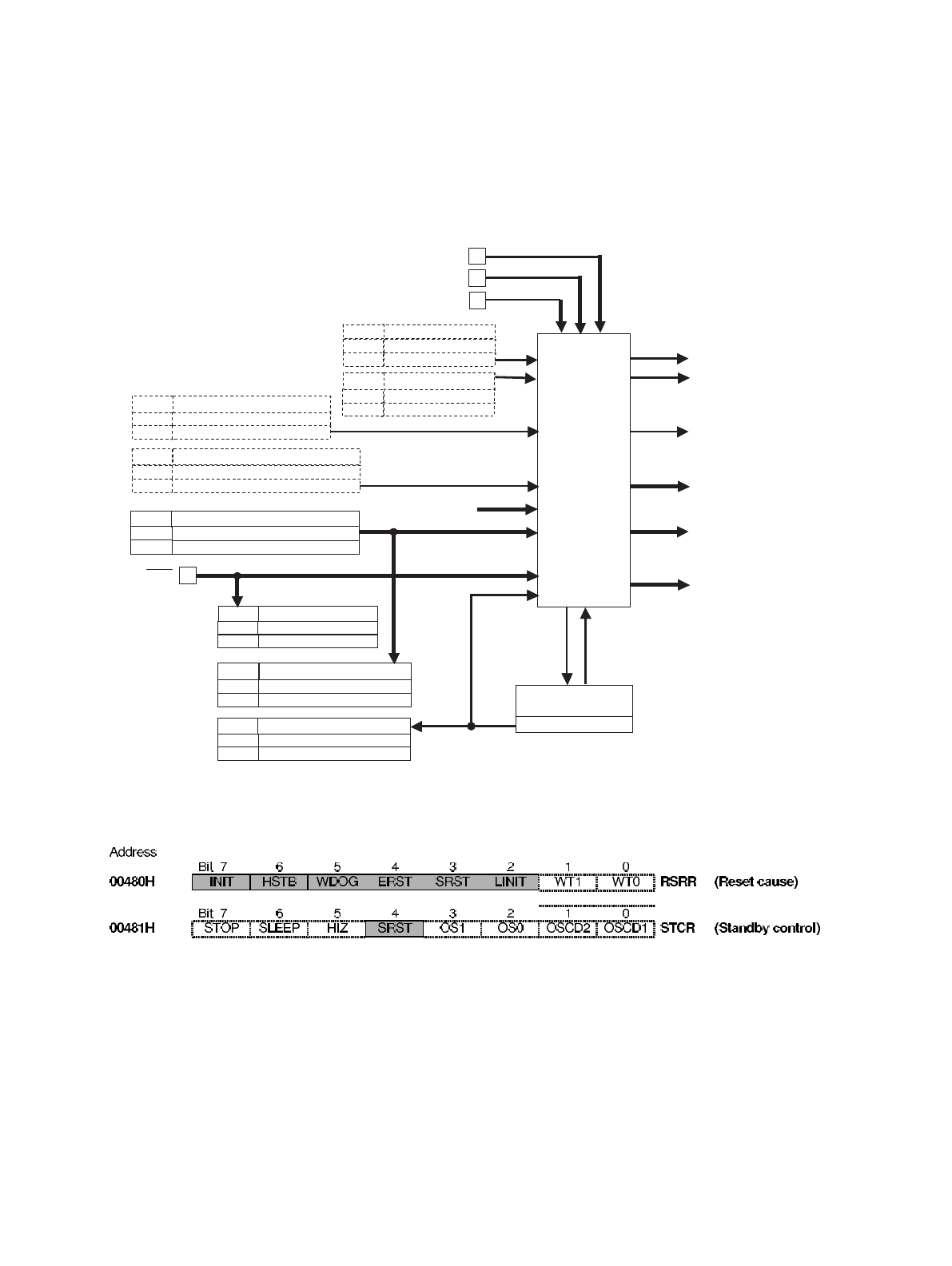

Figure 3-1 Configuration Diagram

Figure 3-2 Register List

Sleep signal

WDOG

0

1

RSRR: bit5

(INIT)

SRST

0

1

RSRR: bit

RST)

RST)

0

1

RSRR: bit7

Oscillation stabilization wait ended

Clear counter and

start oscillation

stabilization wait

Time-base counter

(oscillation stabilization wait)

SRST

0

1

STCR: bit4

INIT

Stop signal

Clock control

Pin control

Initialization reset (INIT)

Operation reset (RST)

Internal interrupts, external interrupts

STOP

0

1

STCR: bit7

SLEEP

0

1

STCR: bit7

OSCD1

0

1

STCR: bit1

HIZ

0

1

STCR: bit0

State transition control circuit (reset related)

State

transition

control

circuit

0

1

RSRR: bit5

No watchdog timeout

Watchdog timeout (INIT) occurred

0

1

RSRR: bit3

No software reset (RST)

Software reset (RST) occurred

0

1

RSRR: bit7

INIT

No INIT pin input

Watchdog timer

0

1

STCR: bit4

Trigger software reset

Do not trigger software reset

STOP

0

1

STCR: bit7

0

1

STCR: bit7

Do not change to stop mode

Change to stop mode

0

1

STCR: bit7

Do not change to sleep mode

Change to sleep mode

0

1

STCR: bit1

Main clock continues to operate during stop mode

Main clock halts during stop mode

0

1

STCR: bit0

Maintain pin states during stop mode

Set pins to high impedance during stop mode

MOD0

MOD1

MOD2

INIT pin input occurred

RSRR/STCR