317

Chapter 24 Interrupt Control

4.Registers

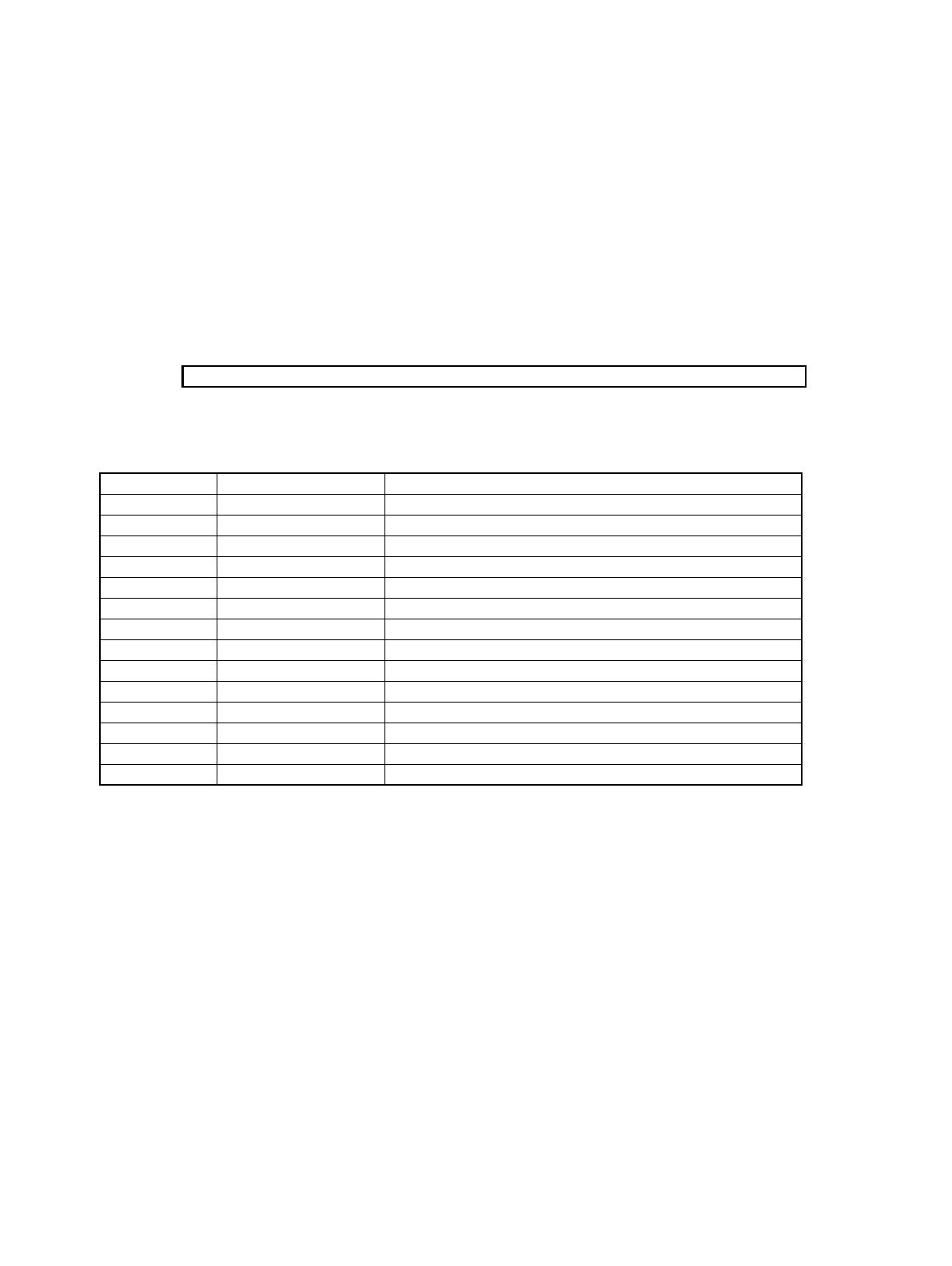

4.2 Interrupt Vector

Interrupt vector that corresponds to a vector number (#) with TBR register set to 0FFC00h (initial value):

• Set the address of each interruption handling routine to the corresponding vector.

• The address of a vector = TBR (table vector register) + {3FCH - 4 x vector number (#)}

• EIT used by system (#0-#14)

#00 : Address FFFBCh

#01 : Address FFFB8h

~

~

~

#07 : Address FFFE0h

~

~

~

#63 : Address FFF00h

~

~

~

#143 : Address FFDC0h

32 bits

Interrupt number Interrupt level (fixed) Factor

#0 0 Reset vector

#1 1 Mode vector

#2-#4 – Reserved for system

#5 5 CPU Supervisor Mode

#6 6 Memory Protection Exception

#7 7 Coprocessor absence trap

#8 8 Coprocessor error trap

#9 9 INTE instruction

#10 10 Instruction break exception

#11 11 Operand break trap

#12 12 Step trace trap

#13 13 MNI request (TOOL)

#14 14 Undefined-instruction exception

#15 15 NMI request