578

Chapter 31 External Bus

7.Address/data Multiplex Interface

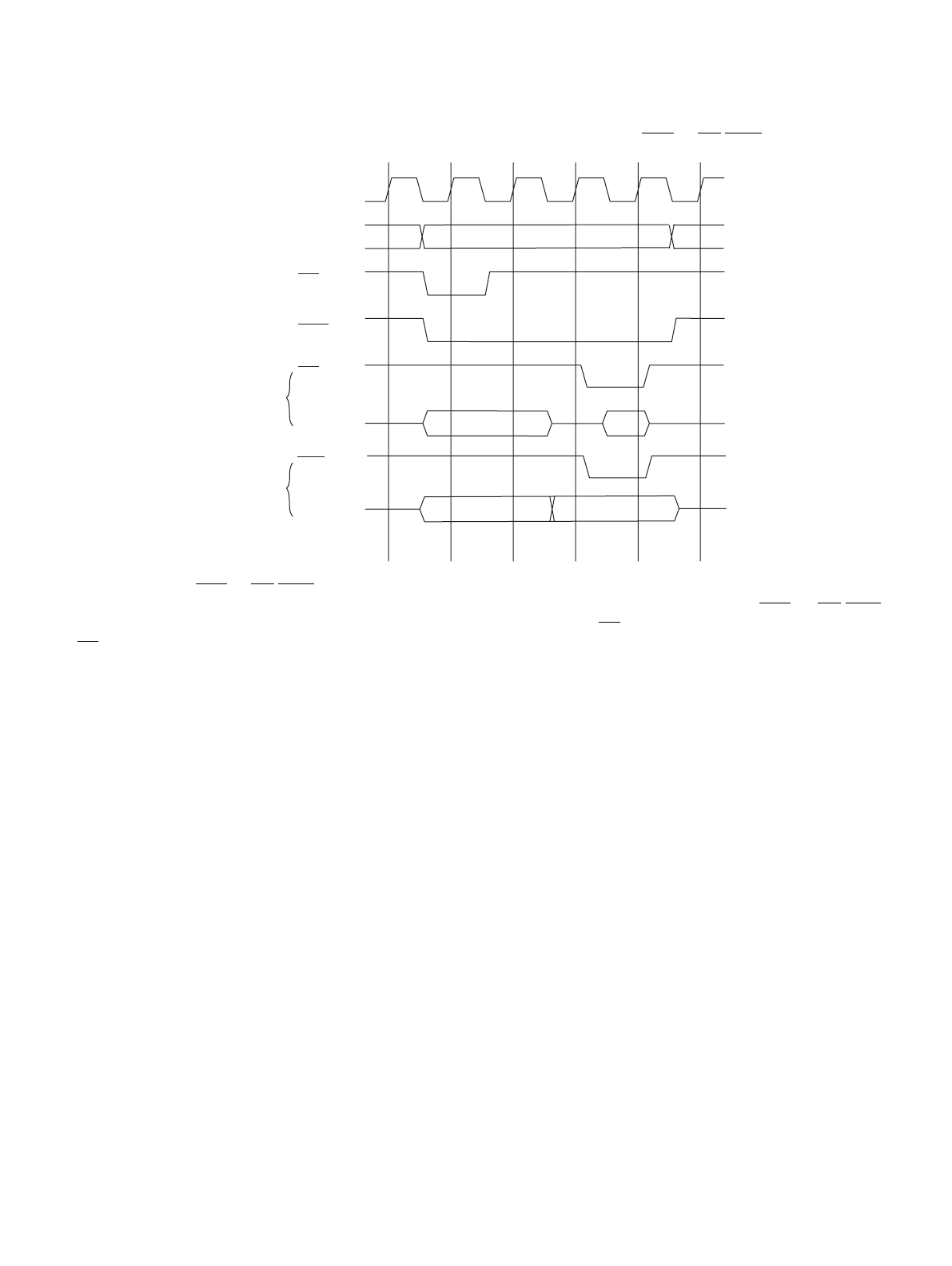

Figure 7-3 Timing Chart for the Address/Data Multiplex Interface (CSn -> RD/WRn Setup)

Setting 1 for the CSn -> RD/WRn setup delay (AWR1) enables the multiplex address output cycle to be extended

by one cycle as shown in Figure 7-3 "Timing Chart for the Address/Data Multiplex Interface (CSn -> RD/WRn

Setup)", allowing the address to be latched directly to the rising edge of AS. Use this setting if you want to use

AS as an ALE (Address Latch Enable) strobe without using MCLK.

address[31:0]

address[15:0]

address[15:0]

data[15:0]

data[15:0]

MCLK

AS

CSn

RD

A[31:0]

D[31:16]

D[31:16]

WR

WRITE

READ