550

Chapter 31 External Bus

4.Endian and Bus Access

● Halfword access

The byte data on the MSB side for the big endian address 0 becomes byte data on the LSB side when the little

endian method is used.

For halfword access, the byte locations of two bytes are reversed.

0 -> 1, 1 -> 0

● Byte access

There is no difference between little endian and big endian.

■ Restrictions on the Little Endian Area

• If prefetch is enabled for a little endian area, always use word access to access the area. If data written to the

prefetch buffer is accessed with any length other than word length, the correct endian conversion is not

performed and the wrong data will be read. The reason is hardware restrictions related to the endian

conversion mechanism.

• Do not place any instruction code in a little endian area.

■ Data Format

The relationship between the internal register and external data bus is as follows:

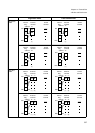

Figure 4-14 Relationship between the Internal Register and External Data Bus for Word Access

Figure 4-15 Relationship between Internal Register and External Data Bus for Halfword Access

D31

D15

D23

D7

D0

AA

BB

CC

DD

Internal register

D31

D15

D23

D7

D0

AA

BB

CC

DD

External bus

(1) Word access (when executing the LD/ST instructions)

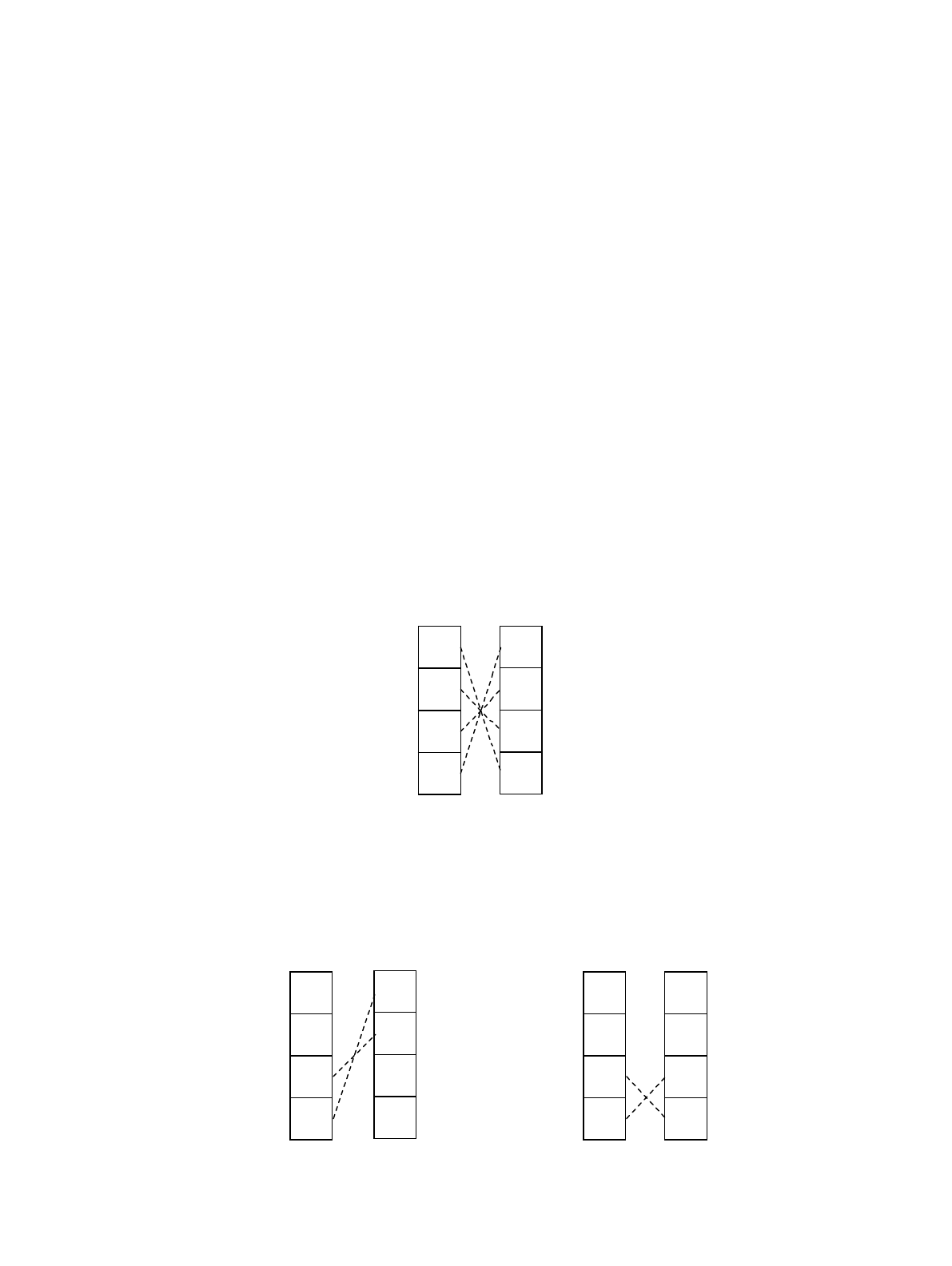

D31

D15

D23

D7

D0

AA

BB

D31

D15

D23

D7

D0

AA

BB

D31

D15

D23

D7

D0

AA

BB

D31

D15

D23

D7

D0

AA

BB

(2) Halfword access (when executing the LDUH/STH instructions)

a) Output address low-order digits "00" b) Output address low-order digits "10"

Internal register External bus Internal register External bus