700

Chapter 34 CAN Controller

2.Register Description

The LEC field holds a code which indicates the type of the last error to occur on the CAN bus. This field will be

cleared to ‘0’ when a message has been transferred (reception or transmission) without error. The unused

code ‘7’ may be written by the CPU to check for updates.

■ Status Interrupts

A Status Interrupt is generated by bits BOff and EWarn (Error Interrupt) or by RxOk, TxOk, and LEC (Status

Change Interrupt) assumed that the corresponding enable bits in the CAN Control Register are set. A change

of bit EPass or a write to RxOk, TxOk,or LEC will never generate a Status Interrupt.

Reading the Status Register will clear the Status Interrupt value (8000h) in the Interrupt Register, if it is

pending.

■ Error Counter (ERRCNT)

5 Bit0Error During the transmission of a message (or acknowledge bit or active

error flag, or overload flag), the device wanted to send a dominant

level (data or identifier bit logical value ‘0’), but the monitored Bus

value was recessive. During busoff recovery this status is set each

time a sequence of 11 recessive bits has been monitored. This

enables the CPU to monitor the proceeding of the busoff recovery

sequence (indicating the bus is not stuck at dominant or continuously

disturbed).

6

CRCError

The CRC check sum was incorrect in the message received, the

CRC received for an incoming message does not match with the cal-

culated CRC for the received data.

7

unused

When the LEC shows the value ‘7’, no CAN bus event was detected

since the CPU wrote this value to the LEC.

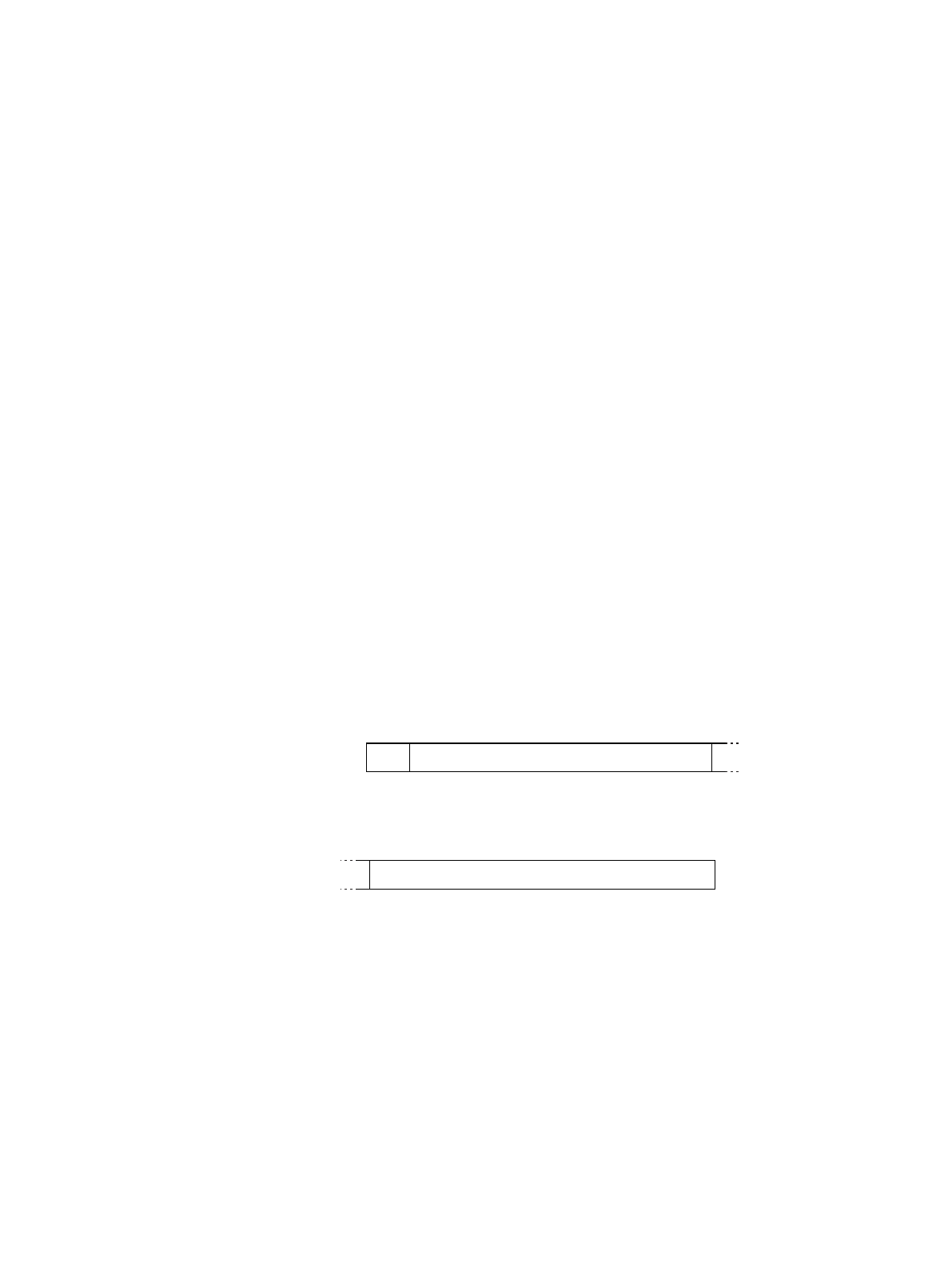

RP REC6-0

⇐ Bit no.

Read/write ⇒

(R) (R) (R) (R) (R) (R) (R) (R)

Default value⇒

(0) (0) (0) (0) (0) (0) (0) (0)

Error Counter high byte

Address : Base + 0x04

H

15 14 13 12 11 10 9 8

ERRCNTH

TEC7-0

⇐ Bit no.

Read/write ⇒

(R) (R) (R) (R) (R) (R) (R) (R)

Default value⇒

(0) (0) (0) (0) (0) (0) (0) (0)

Address :

Base + 0x

05H

765432 10

ERRCNTL

Error Counter low byte