692

Chapter 34 CAN Controller

2.Register Description

2. Register Description

This section lists the CAN registers and describes the function of each register in detail.

2.1 Programmer’s Model

The CAN module allocates an address space of 256 bytes (64 words). The CAN registers can be accessed

from the CPU in byte, halfword and word.

The two sets of interface registers (IF1 and IF2) control the CPU access to the Message RAM. They buffer the

data to be transferred to and from the RAM, avoiding conflicts between CPU accesses and message

reception/transmission.

The data registers (IF1 Data and IF2 Data) are doubled in the address map, ordered both in little endian byte

and big endian byte.

If several CAN modules are present on a device then they are located linear in the address space with a

constant offset of 256 bytes (64 words). The base address of each CAN module is given by the following

table:

• Base-address of CAN0 :0x00C000

• Base-address of CAN1 :0x00C100

• Base-address of CAN2 :0x00C200

• Base-address of CAN3 :0x00C300

• Base-address of CAN4 :0x00C400

• Base-address of CAN5 :0x00C500

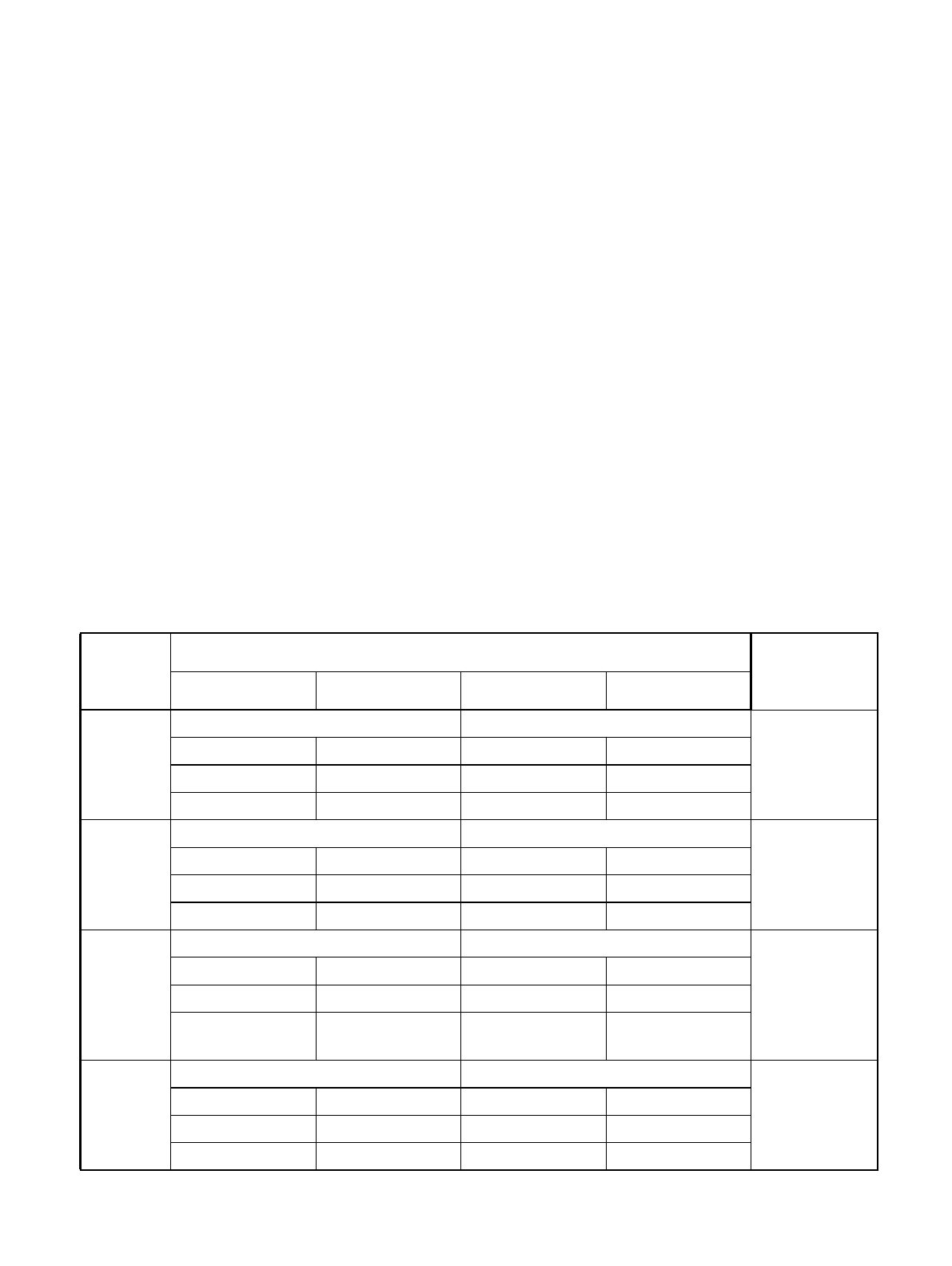

Address

Register

Note

+0 +1 +2 +3

Base-addr +

0x00

Control Register Status Register

bit[15:8] bit[7:0] bit[15:8] bit[7:0]

reserved see descr. CTRLR reserved see descr. STATR

Reset: 0x00 Reset: 0x01 Reset: 0x00 Reset: 0x00

Base-addr +

0x04

Error Counter Bit Timing Register ErrorCounter isread

only.

Bit Timing Register

is write enabled by

CCE

bit[15:8] bit[7:0] bit[15:8] bit[7:0]

RP,REC[6:0] TEC[7:0] TSeg2[2:0],TSeg1[3:0] SJW[1:0],BRP[5:0]

Reset: 0x00 Reset: 0x00 Reset: 0x23 Reset: 0x01

Base-addr +

0x08

Interrupt Register Test Register Interrupt Register is

read only.

Test Register iswrite

enabled by Test.

r signifies the actual

value of the

CAN_RX pin.

bit[15:8] bit[7:0] bit[15:8] bit[7:0]

Int-Id[15:8] Int-Id[7:0] reserved see descr. TESTR

Reset: 0x00 Reset: 0x00 Reset: 0x00 Reset: 0x00 &

0br0000000

Base-addr +

0x0C

BRP Extension Register Reserved BRP Extension Reg-

ister is write enabled

by CCE.

bit[15:8] bit[7:0] bit[15:8] bit[7:0]

reserved BRP[3:0] reserved reserved

Reset: 0x00 Reset: 0x00 Reset: 0x00 Reset: 0x00