237

Chapter 16 Clock Supervisor

4.Operation Modes

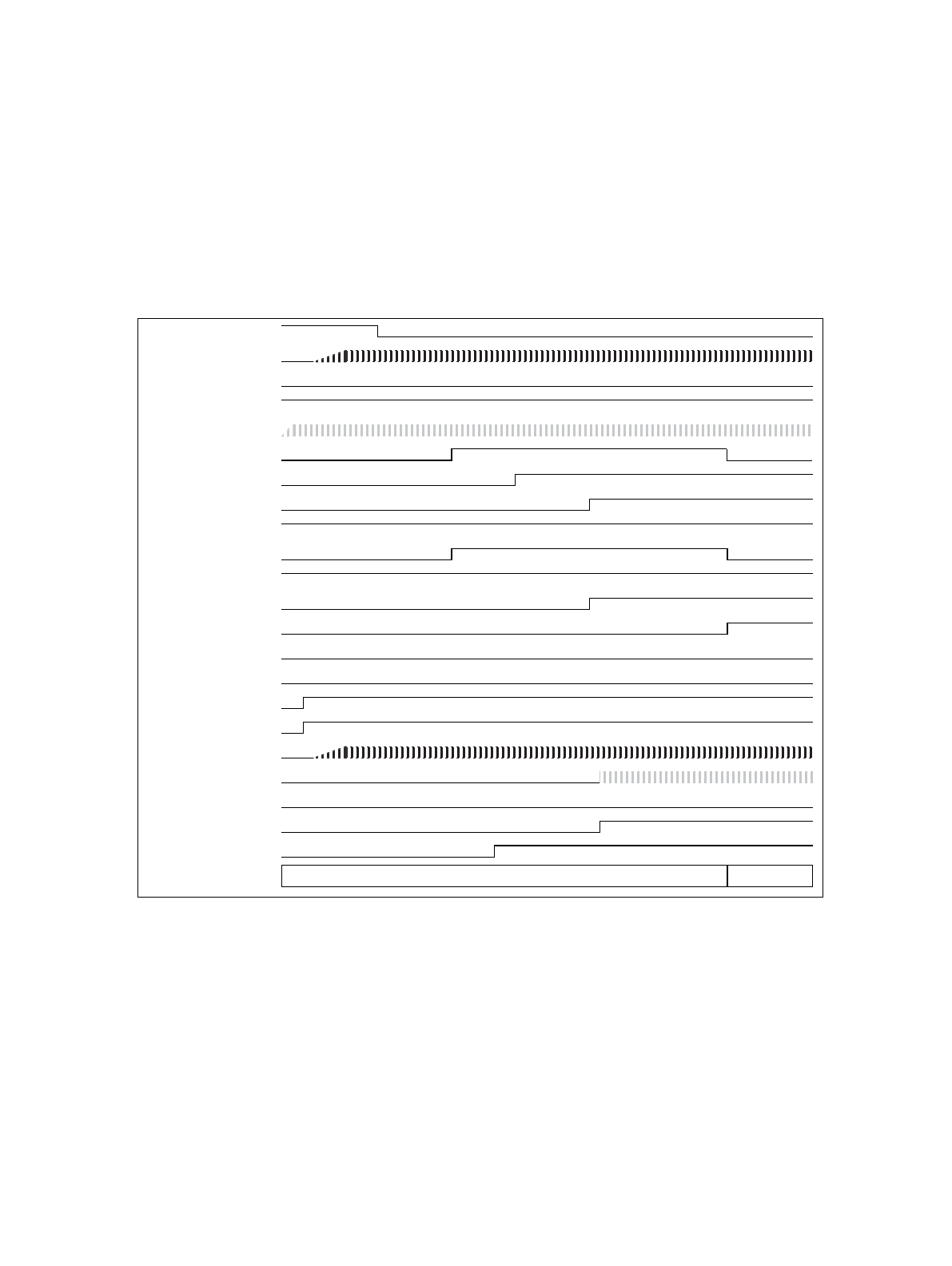

■ Operation with single clock device

In a single clock device the sub-clock supervisor can provide the RC-oscillation clock as sub-clock. To enable this

feature, SCKS bit (bit7 of CSVCR) must be set to ’1’ (refer to Table 2-1for precautions when modifying this bit)

and SRST must be ’0’ (initial value). Before the transition to sub-clock mode, it has to be confirmed by software

that the sub-clock has been substituted by the RC-oscillation clock. This can be accomplished by checking that

SM bit (bit 5 of CSVCR) is ’1’ and RCE bit (bit 4 of CSVCR) is ’1’.

Figure 4-12 Timing Diagram: Sub-clock mode with single clock device

PONR

MCLK

SCLK

RC_CLK

OSC_STAB

MSVE

MSEN

SSVE

SSEN

MCLK_STBY

SCLK_STBY

TO_MCLK

TO_SCLK

EXT_RST

EXT_RST_OUT

MCLK_OUT

SCLK_OUT

MCLK_MISSING

SCLK_MISSING

SRST

RCE

SCKS

Main Sub

Clock Mode