531

Chapter 31 External Bus

2.External Bus Interface Registers

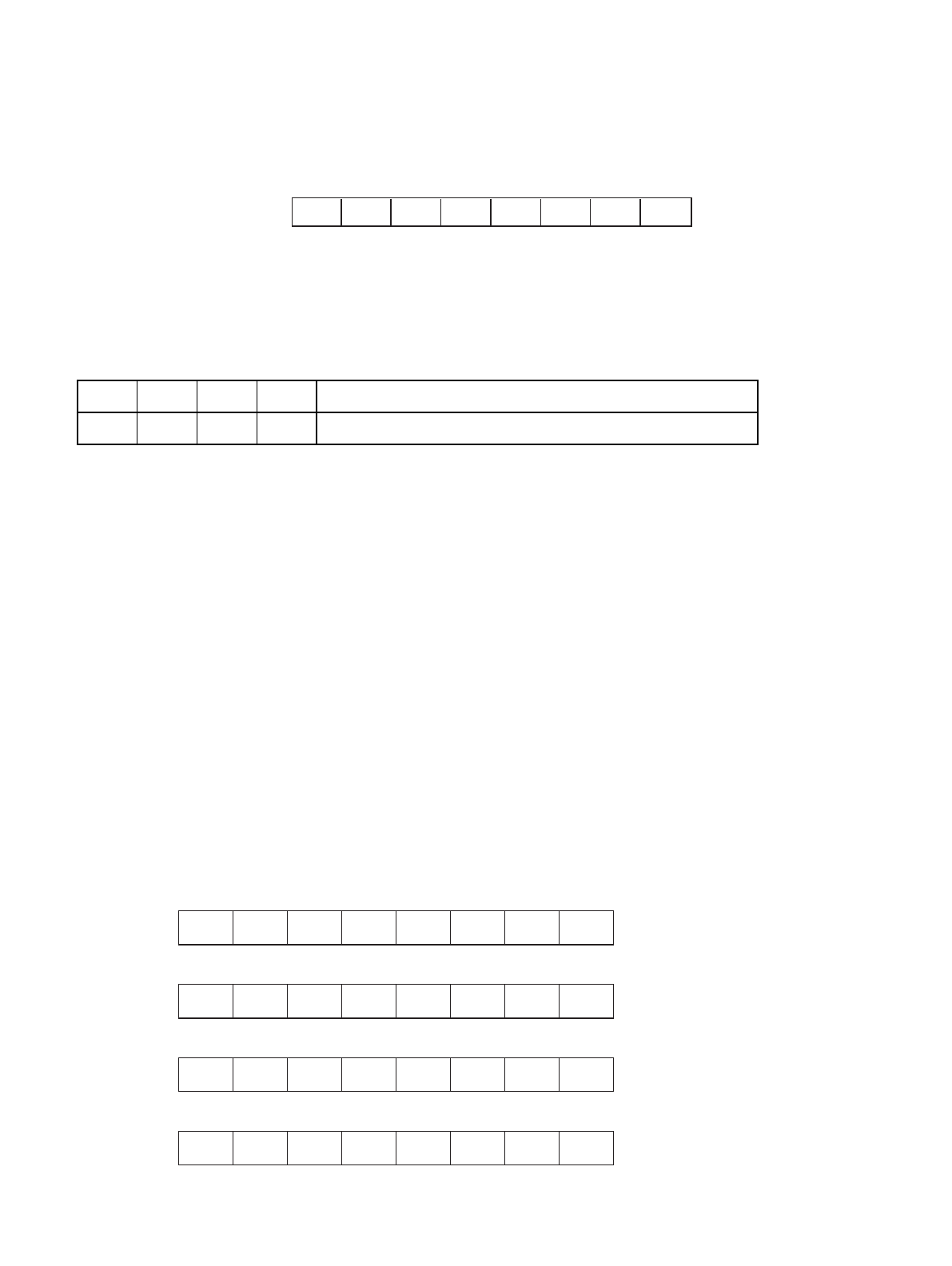

Figure 2-5 Structure of the Memory Setting Register (MCRB for FCRAM auto - precharge ON mode)

The register serves as the area for making various settings for FCRAM connected to the chip select area for

which the access type (TYP3 to TYP0 bits) in the ACR6 and ACR7 registers has been set as in Table 2-30 .

Table 2-30 lists the access type settings (TYP3 to TYP0 bits).

MCRB shares register hardware with MCRA. Updating the MCRB therefore updates the MCRA accordingly.

The functions are the same as MCRA. Note, however, that the function of the WBST bit is not available to this

TYPE setting.

(FCRAM supports neither burst read nor single write mode.)

2.6 I/O Wait Registers for DMAC (IOWR0-3)

This section explains the configuration and functions of the I/O wait registers for DMAC (IOWR0-

3).

■ Configuration of the I/O Wait Registers for DMAC (IOWR0-3)

The I/O wait registers for DMAC (IOWR0-3: I/O Wait Register for DMAC 0-3) set various kinds of waits during

DMA fly-by access.

Figure 2-6 "Configuration of the I/O wait registers for DMAC (IOWR0, 1, 2, 3)" shows the configuration of the I/O

wait registers for DMAC (IOWR0-3).

Figure 2-6 Configuration of the I/O Wait Registers for DMAC (IOWR0-3)

Table 2-21 Access type settings (TYP3 to TYP0 bits)

TYP3 TYP2 TYP1 TYP0 Access type

1001Memory type B: FCRAM (used auto precharge)

23 22 21 20 19 18 17 16

00000671

H

Reserved PSZ2 PSZ1 PSZ0 WBST BANK ABS1 ABS0

Initial value

Address

bit

XXXXXXXX

B

(INIT)

XXXXXXXX

B

(RST)

R/W R/W R/W R/W R/W R/W R/W R/W

IOWR0

IOWR1

IOWR2

IOWR3

31 30 29 28 27 26 25 24

0000 0678

H

RYE0 HLD0 WR01 WR00 IW03 IW02 IW01 IW00

0000 0679

H

RYE1 HLD1 WR11 WR10 IW13 IW12 IW11 IW10

0000 067a

H

RYE2 HLD2 WR21 WR20 IW23 IW22 IW21 IW20

76543210

0000 067b

H

RYE3 HLD3 WR31 WR30 IW33 IW32 IW31 IW30

23 22 21 20 19 18 17 16

15 14 13 12 11 10 9 8

xxxxxxxx

b

xxxxxxxx

b

xxxxxxxx

b

xxxxxxxx

b

xxxxxxxx

b

xxxxxxxx

b

xxxxxxxx

b

xxxxxxxx

b

W/R

W/R

W/R

W/R

Initial value

INIT RST Access