368

Chapter 26 DMA Controller

3.DMA Controller (DMAC) Operation

3.11 Channel Selection and Control

Up to five channels can be simultaneously set as transfer channels. In general, an independent

function can be set for each channel.

■ Priority Among Channels

Since DMA transfer is possible only on one channel at a time, priority must be set for the channels.

Two modes, fixed and rotation, are provided as the priority settings and can be selected for each channel group

(described later).

● Fixed mode

The order of priority is fixed by channel number, with priority decreasing from channel 0 to channel 4:

(ch.0 > ch.1 > ch.2 > ch.3 > ch.4)

If a transfer request with a higher priority is received during a transfer, the transfer channel becomes the channel

with the higher priority when the transfer for the transfer unit (number set in the block size specification register x

data width) ends.

When higher priority transfer is completed, transfer is restarted on the previous channel.

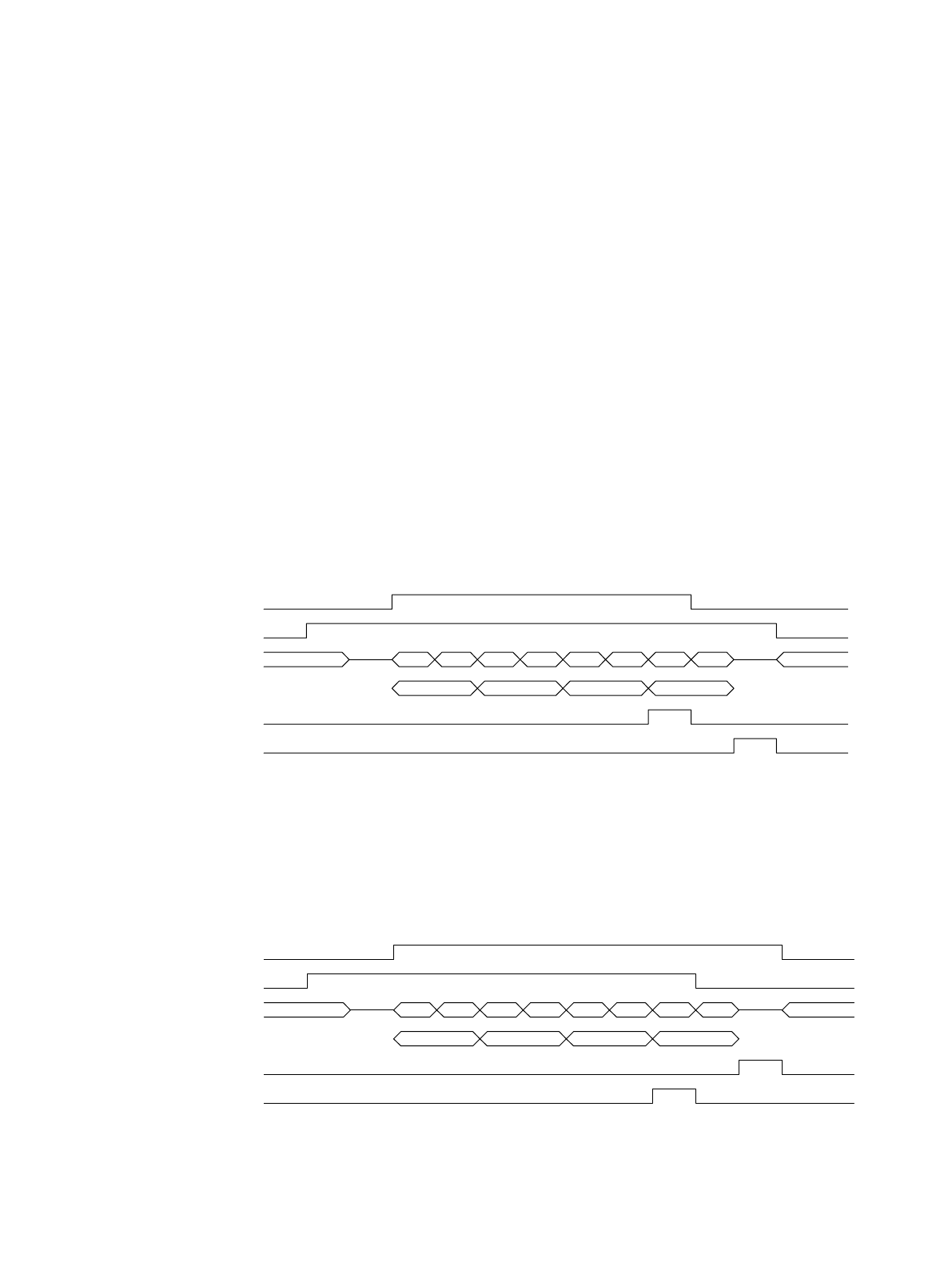

Figure 3-5 Timing Example in Fixed Mode

● Rotation mode (ch.0 to ch.1 only)

When operation is enabled, the initial states have the same order that they would have in fixed mode, but at the

end of each transfer operation, the priority of the channels is reversed. Thus, if more than one transfer request is

output at the same time, the channel is switched after each transfer unit.

This mode is effective when continuous or burst transfer is set.

Figure 3-6 Timing Example in Rotation Mode

CPU SA DA SA DA SA DA SA DA CPU

ch1 ch0 ch0 ch1

ch0 transfer request

ch1 transfer request

Bus operation

Transfer ch

ch0 transfer end

ch1 transfer end

CPU SA DA SA DA SA DA SA DA CPU

ch1 ch0 ch1 ch0

ch0 transfer request

ch1 transfer request

Bus operation

Transfer ch

ch0 transfer end

ch1 transfer end