178

Chapter 11 Memory Controller

8.Explanations of Registers

● FLASH Memory Adddress Check register (FMAC)

This register captures the address at the begin of a FLASH access cycle for test purposes.

The register could be read only.

● Non-cacheable area definition

The non-cacheable area definition registers FCHA0 and FCHA1 define the FLASH region not to be cached. Not

used bits are read back as zero. The tables below define the initial values of the registers. The point defined by

FCHA0 = 0 and mask bits off is located outside the FLASH region, thus initially the whole FLASH region will be

cached.

If the FCHCR_REN bit is cleared, the address range is defined by the address given by FCHA0, masked with the

bits set to ’1’ in FCHA1.

Example 1 (Point and mask range definition):

- FCHCR_REN = 0

- FCHA0 = 0x000F:A300

- FCHA1 = 0x0000:FFFF

The non-cacheable area is defined from 0x000F:0000 to 0x000F:FFFF.

Example 2 (Point to point range definition):

- FCHCR_REN = 1

- FCHA0 = 0x000F:A300

- FCHA1 = 0x000F:F7FF

The non-cacheable area is defined from 0x000F:A300 to 0x000F:F7FF.

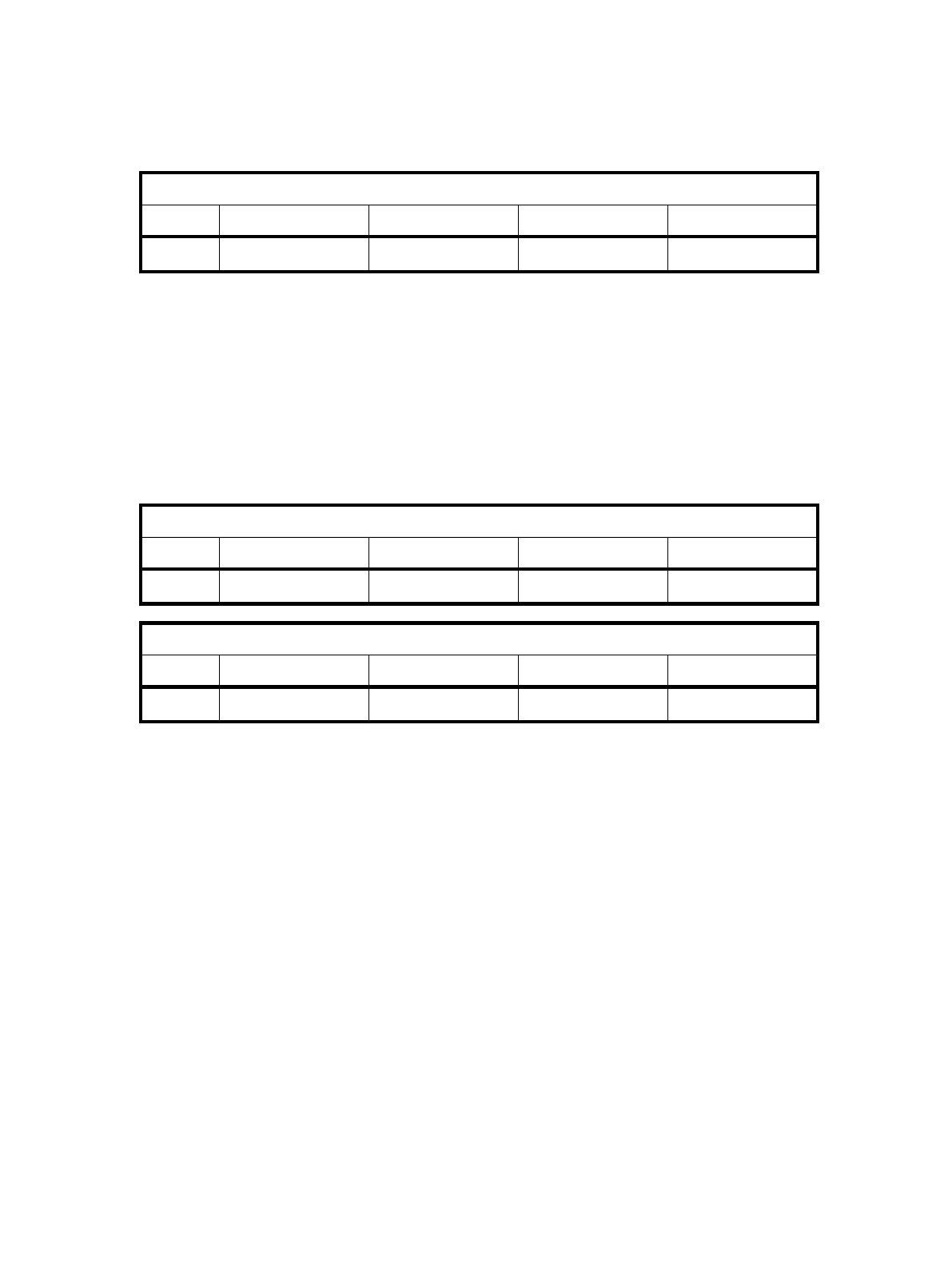

FMAC [R]

Address +0 +1 +2 +3

7008

H

-------- -0000000 00000000 00000000

FCHA0 [R/W]

Address +0 +1 +2 +3

700C

H

-------- -0000000 00000000 00000000

FCHA1 [R/W]

Address +0 +1 +2 +3

7010

H

-------- -0000000 00000000 00000000