826

Chapter 40 Pulse Frequency Modulator

2.Reload Counter Registers

2. Reload Counter Registers

This section describes the 16-bit pulse frequency modulator registers listed below.

Control status register (P0TMCSR, P1TMCSR)

16-bit counter register (P0TMR, P1TMR)

16-bit reload register (P0TMRLR, P1TMRLR)

■ Control Status Register (P0TMCSR, P1TMCSR)

Controls the operation mode and interrupts for the 16-bit reload counter.

Only change the value of bits other than UF and TRG when CNTE = "0".

The bits can be written simultaneously.

● P0TMCSR, P1TMCSR structure

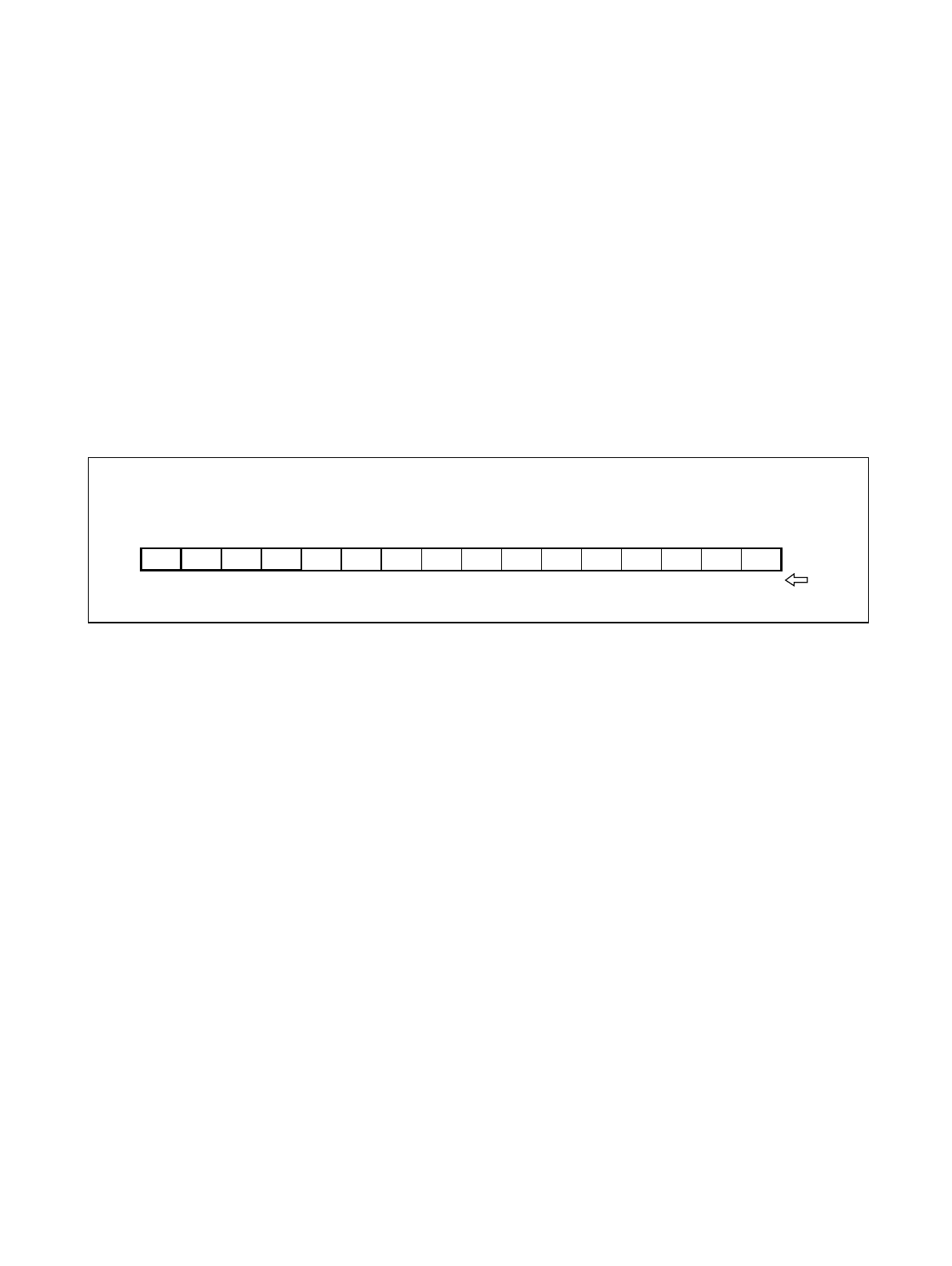

Figure 2-1 Structure of the Control Status Register

● Functions of the P0TMCSR, P1TMCSR bits

[Bit 15] Reserved

Always set to "0".

[Bit 14] INV (INVersion)

The output signal inversion bit.

"0" is default level (counter 0 high level, counter 1 low level).

"1" inverts the output signal (counter 0 low level, counter 1 high level).

Remark: Writing INV of P0TMCSR or INV of P1TMCSR or both has the same effect.

[Bit 13] Reserved

Always set to "0".

[Bits 12, 10] CSL2, CSL1, CSL0 (Count clock SeLect)

The count clock select bits.

Table 2.1 lists the clock source selections.

CSL1

11

CSL0

10

Reserved

9 8

Access

Bits

R/W R/W R/W R/W

RELD

4

INTE

3

UF

2

CNTE

1

TRG

0

Reserved

7

Reserved

6

Reserved

5

R/W R/W R/W R/W R/WR/W R/W R/W

Initial value : -0-000-0 ---00000H

15

INV

14

Reserved

13 12

R/W R/W R/W R/W

Reserved

CSL2

0000 0170

H

Address

0000 0172

H

MOD1