199

Chapter 13 Clock Control

5.Operation

5. Operation

This section describes how to setup and switch between clocks.

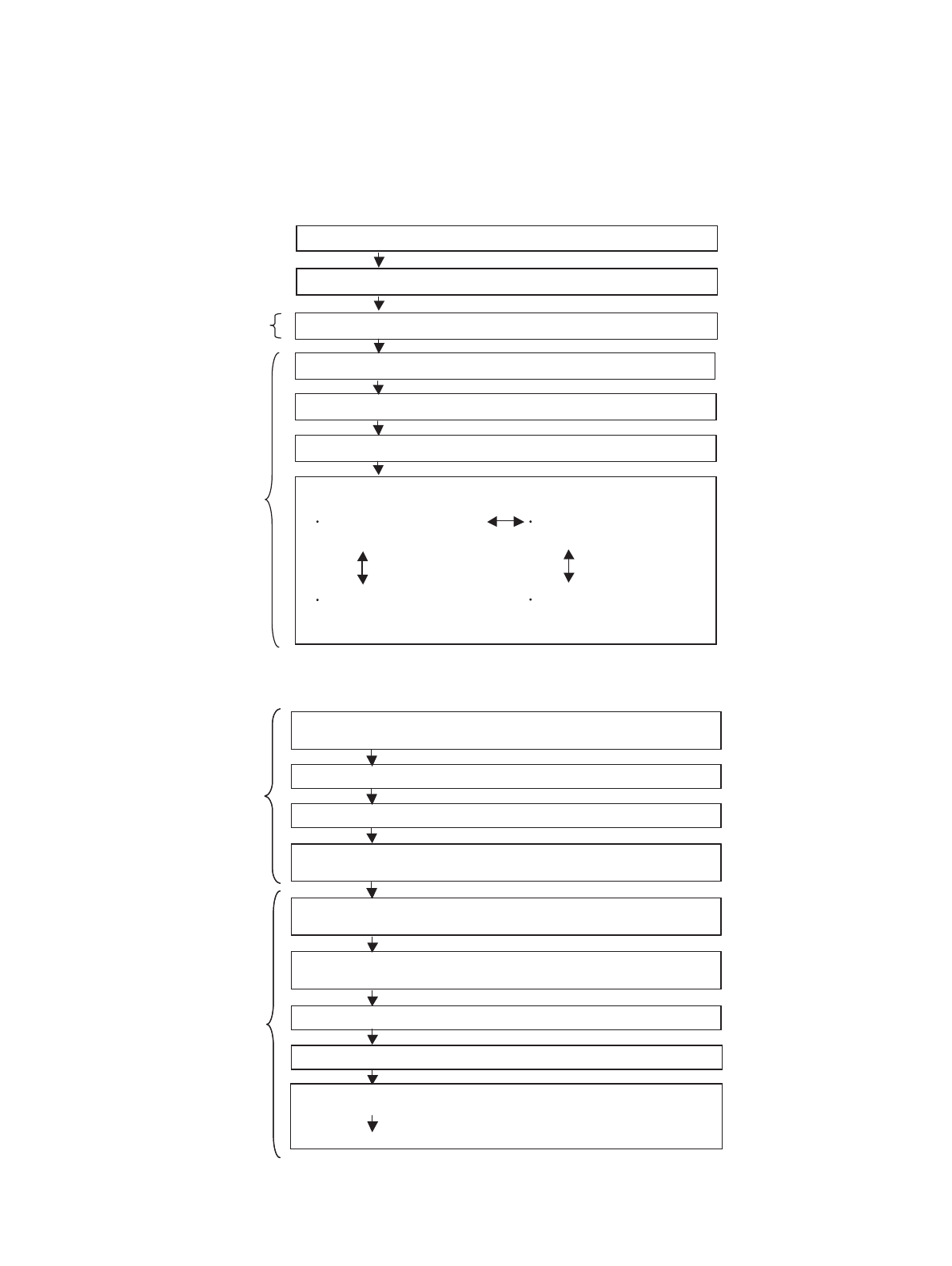

5.1 Clock Setup Sequence (Example)

5.2 Halting and Restarting the Main Clock Oscillation During Subclock Mode (Example)

(2) Operate using initial values (main clock divided by 2).

(3) Select PLL multiplier. ( PLLS[2:0] )

(4) Enable main PLL operation (PLL1EN), and enable sub clock operation (PLL2EN).

(1) Main clock oscillation stabilization, sub clock oscillation stabilization

(5) Select clock source. (CLKS[1:0] )

Main clock mode (divided by 2)

Main clock mode (divided by 2)

(“01”)(“00”)

(“11”)(“10”)

Main PLL mode

Sub clock mode

Setup

base

clock.

(2) Set divide ratios for operating clocks. (CLKB, CLKP, CLKT)

Setup

operating

clocks.

(4) Wait for main PLL to lock (See oscillation stabilization wait chapter).

(1) Select sub clock mode.

Select clock source. (CLKS [1:0] = “11”)

(5) Select main PLL mode.

Select clock source. (CLKS[1:0] = “00”)

Select clock source. (CLKS[1:0] = “11”)

(4) Wait for main PLL to lock (See oscillation stabilization wait chapter)

(2) Halt main PLL (PLL1EN = "0"), halt main clock oscillation (OSCDS1 = "0")

(3) Change to standby mode (See standby chapter.)

(4) Main clock oscillation (OSCDS1 = “0”)

Main clock oscillation stabilization (See oscillation stabilization wait chapter)

(1) Select main clock mode (divided by 2).

Select clock source. (CLKS[1:0] = “01”)

(1) Start main PLL oscillation (PLL1E = “01”)

(3) Recover from standby mode.

Sub clock mode operation

Change to main

PLL operation

Sub clock mode

with main clock

halted

(See standby chapter.)