266

Chapter 19 Timebase Timer

4.Register

• Bit1: Enabling the synchronous reset operation

• Ordinary operation reset: Immediately resets the operation initialization when the operation initialization

reset (RST) request is generated.

Synchronous reset: Resets the operation initialization after all accesses to the bus have stopped.

• Bit0: Synchronous standby operation enable

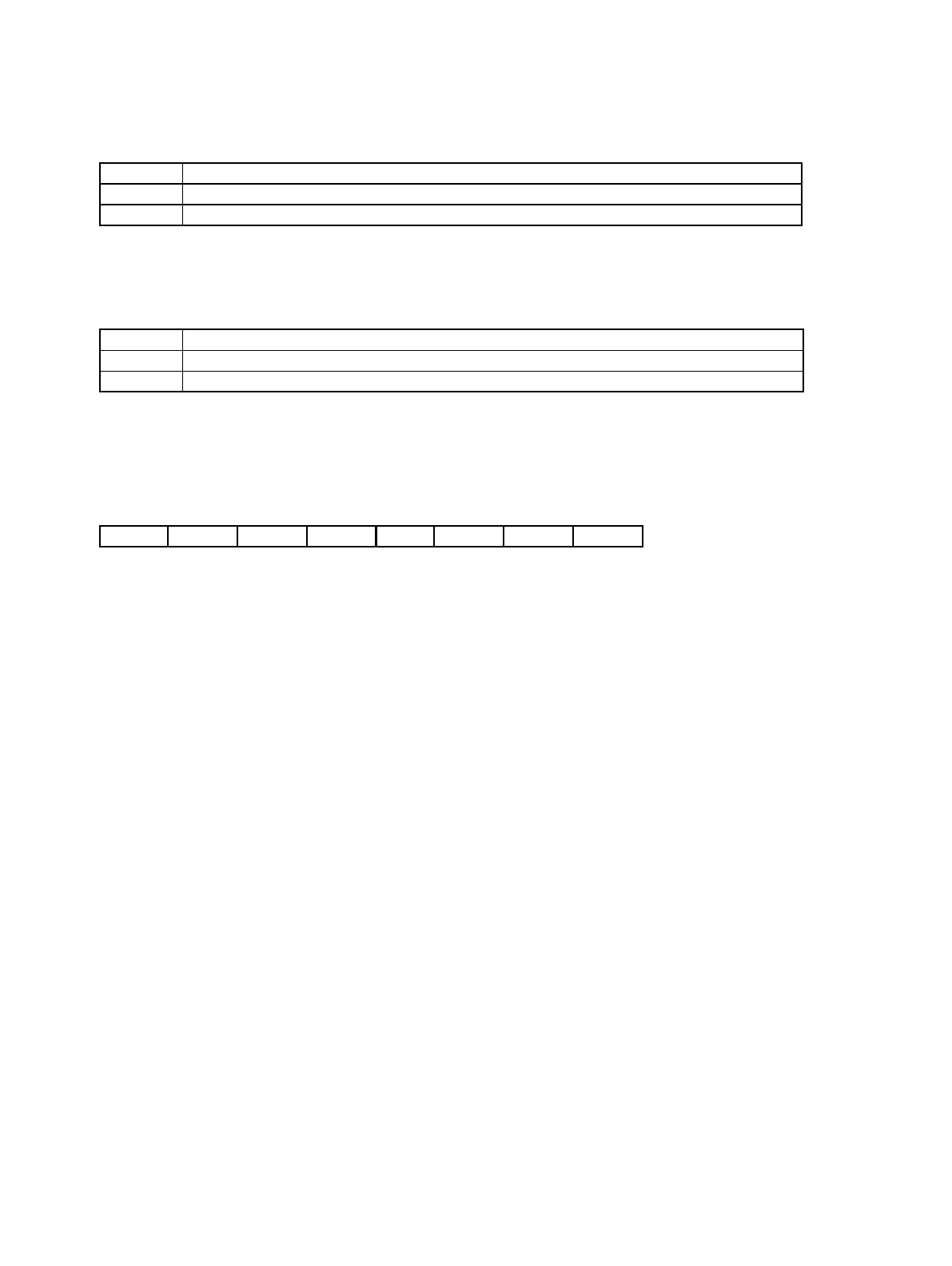

4.2 CTBR: Timebase Counter Clear Register

This register is used to initialize the timebase counter.

• CTBR: Address 0483h (Access: Byte)

(Refer to “Meaning of Bit Attribute Symbols (Page No.10)” for the attributes)

• Continuously writing “A5

H

”, “5A

H

” in the timebase counter clear register clears the timebase counter

immediately after writing “5A

H

”. (All bits are “0”)

There is no time restrictions between “A5

H

” and “5A

H

”, but if “A5

H

” is written followed by the one other than

“5A

H

”, you should write “A5

H

” again. If not, the timebase counter cannot be cleared even if “5A

H

” is written.

• The read value is indefinite.

• Clearing the timebase counter using the timebase counter clear register temporarily modifies the relevant

items shown below.

• Oscillation stability wait interval

• Watchdog timer period

• Timebase timer period

SYNCR Operation

0 Ordinary reset operation

1 Synchronous reset operation enable

SYNCS Operation

0 Ordinary reset operation (In this product, any setting is prohibited)

1 Synchronous standby operation enable (Be sure to set before making the transition to standby)

76543210 bit

D7 D6 D5 D4 D3 D2 D1 D0

X X X X X X X X Initial value

RX/W RX/W RX/W RX/W RX/W RX/W RX/W RX/W Attribute