405

Chapter 29 MPU / EDSU

3.Break Functions

Permissions can be set for the comparator channel CMP1 and CMP0 separately, indicated by the symbol index.

At each time an instruction is executed or an operand is accessed, the actual valid permissions were evaluated.

This evaluation is divided into operand access (OA-based) and code execution (IA-based).

For each part the highest priority region hit is searched for. The highest channel number has the highest priority

(strict priority scheme). If a channel hit was found, the permissions defined for this channel will apply. If no channel

hit was detected, the default permissions apply.

After the actual permissions are evaluated (valid for actual data access, if any, and actual instruction) the permis-

sions were checked. If the exceute permission is not set or if the read or write permissions do not fit to the type of

the actual access, a protection violation will be indicated. This causes a CPU trap to the memory protection violation

MPUPV handler routine. The CPU switches directly to SuperVisor mode in this case.

The config register space of the EDSU is protected against random access in User mode. Only in SuperVisor mode

or Emulation mode the register file enables write access. For configuration a system interrupt INT #5 was defined,

which switches in SuperVisor mode (SV bit remains set during the execution of the INT #5-ISR). Except debugger

interrupts by the emulator and NMI the SuperVisor ISR is not interruptible.

Exceptions caused by the memory protection and the break unit for debugging are separated. In that way the mem-

ory protection functionality can be debugged itself.

3.6 Break Factors

Summary of the internal break factors and the executed events:

Break on instruction address -> Causes Instruction Break

Break on operand address -> Causes Operand Break

Break on data value -> Causes Operand Break

Resource Interrupt (BREAK) -> Causes Tool NMI

Step Trace Trap -> Causes Step Trace Trap

Execution of the INTE instr. -> Causes INTE

Execution of INT #5 -> CPU SuperVisor Mode

Memory protection exception -> Causes MPUPV Trap

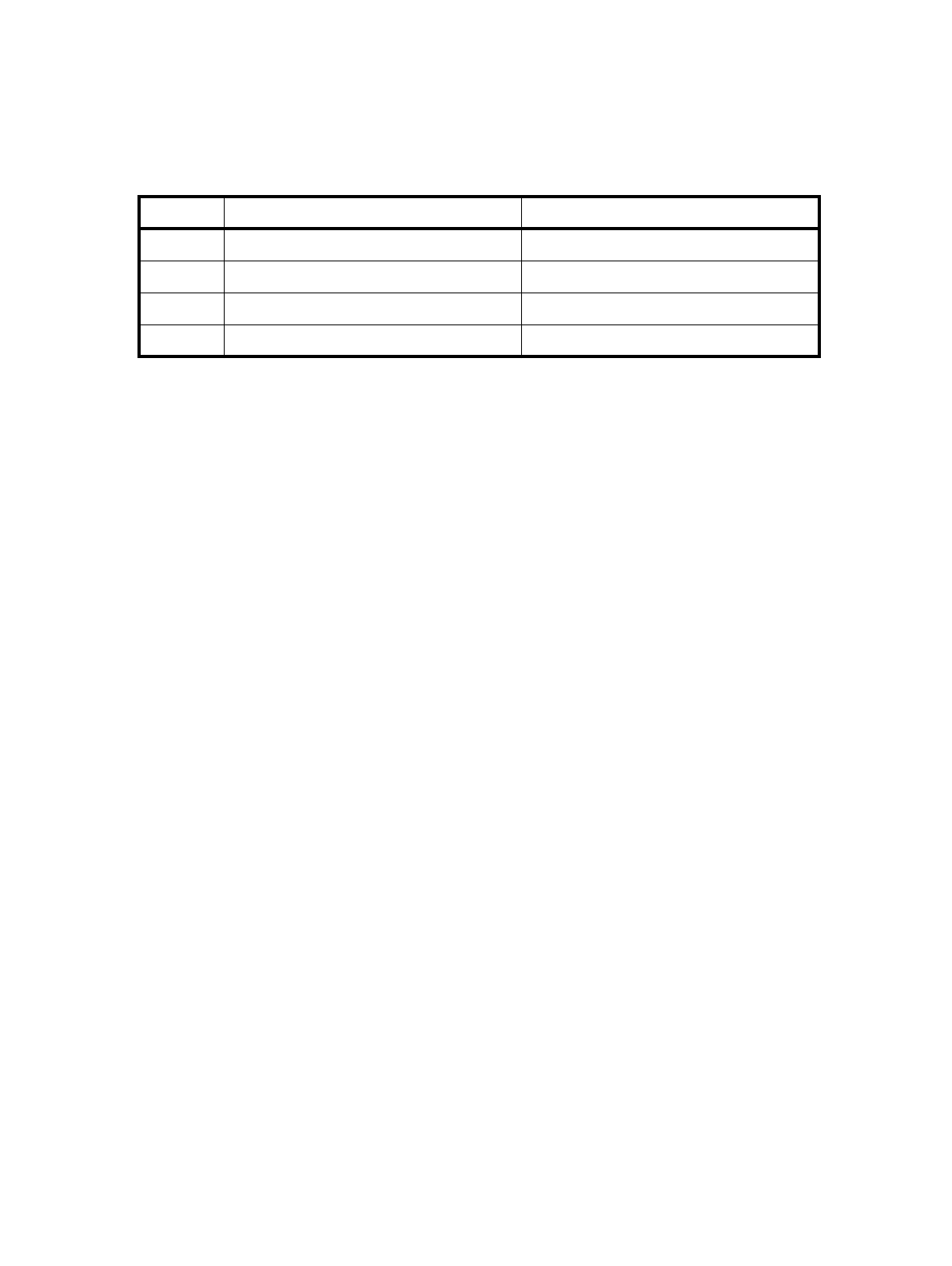

Table 3-7 Meaning of the permission config bits

Symbol Data Mode (OA) Instruction Mode (IA)

SRX[1:0] SuperVisor Read permission SuperVisor eXecute permission

SW[1:0] SuperVisor Write permission -

URX[1:0] User Read permission User eXecute permission

UW[1:0] User Write permission -