792

Chapter 38 Reload Timer

7.Q & A

7.10 How do I generate an activation trigger?

• Generating a soft trigger

The setting is done via the software trigger bit (TMCSR.TRG).

When the software trigger bit (TGR) is set to“1”, a trigger is generated.

To enable operation and activate at the same time, set the count permission bit (TMCSR.CNTE) and the soft trigger bit

(TMCSR.TRG) simultaneously.

• Generating an external trigger

By inputting the edge specified by the trigger selection bit to the trigger pin corresponding to each reload timer, a

trigger is generated.

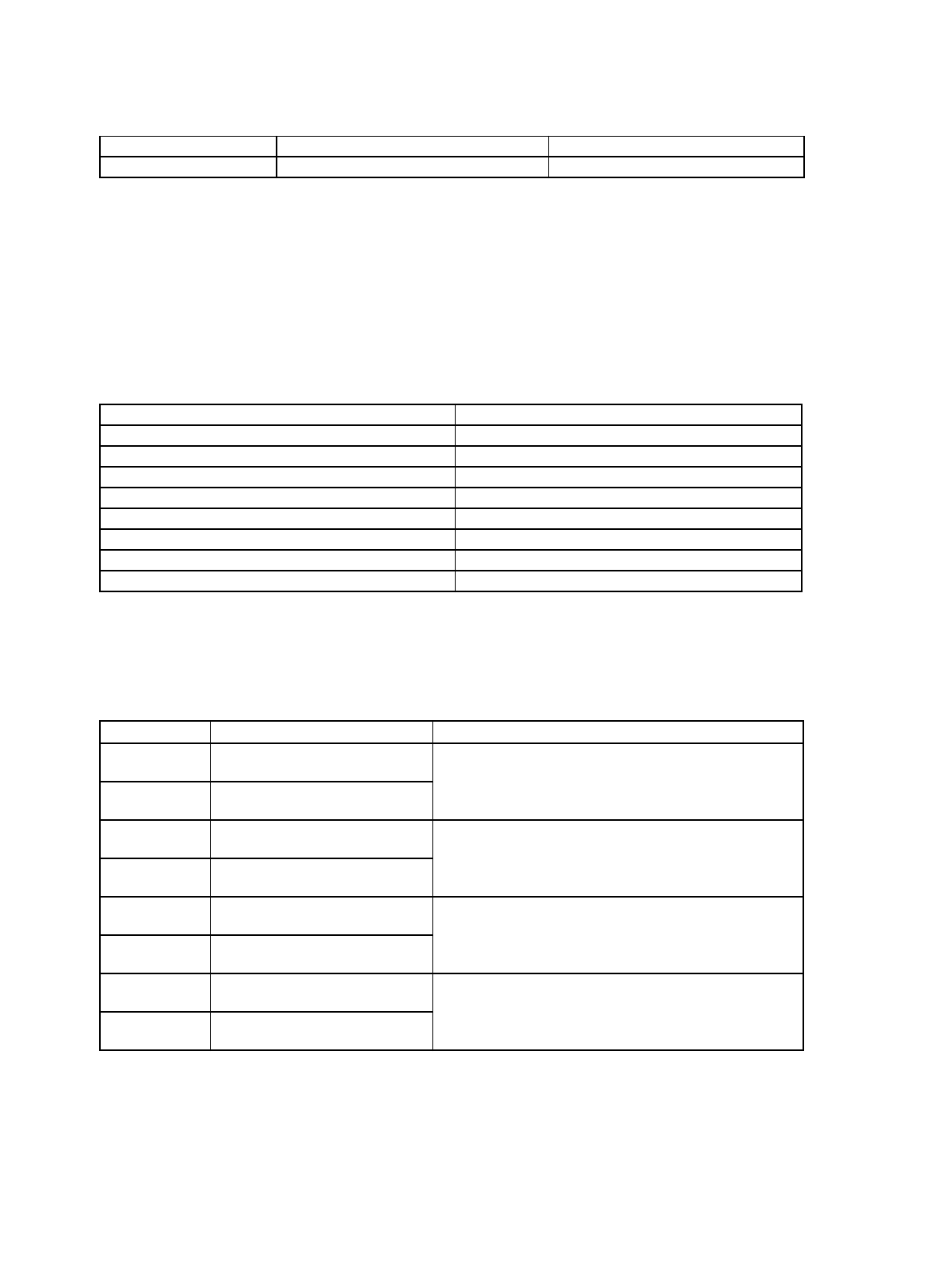

7.11 What are the interrupt-related registers?

The relationship between reload timer numbers, interrupt level, vector, control register, etc is outlined in the

following table.

For details on interrupt level and interrupt vectors, see “Chapter 24 Interrupt Control (Page No.311)”.

Interrupt request flag (TMCSR0.UF) ~ (TMCSR7.UF) is not automatically cleared, so before returning from

interrupt processing, set the UF bit to “0” to reset it.

7.12 How do I enable interrupts?

Enabling interrupts, interrupt request flag

TIN6 pin PFR14.6 = ‘1’ -

TIN7 pin PFR14.7 = ‘1’ -

Timer Trigger pin

Reload timer 0 TIN0

Reload timer 1 TIN1

Reload timer 2 TIN2

Reload timer 3 TIN3

Reload timer 4 TIN4

Reload timer 5 TIN5

Reload timer 6 TIN6

Reload timer 7 TIN7

Interrupt vector (default)

Interrupt level setting bit (ICR[4:0])

Reload timer 0

#32

Address: 0FFF7Ch

Interrupt level register (ICR08)

Address: 0448h

Reload timer 1

#33

Address: 0FFF78h

Reload timer 2

#34

Address: 0FFF74h

Interrupt level register (ICR09)

Address: 0449h

Reload timer 3

#35

Address: 0FFF70h

Reload timer 4

#36

Address: 0FFF6Ch

Interrupt level register (ICR10)

Address: 044Ah

Reload timer 5

#37

Address: 0FFF68h

Reload timer 6

#38

Address: 0FFF64h

Interrupt level register (ICR11)

Address: 044Bh

Reload timer 7

#39

Address: 0FFF60h