779

Chapter 38 Reload Timer

4.Registers

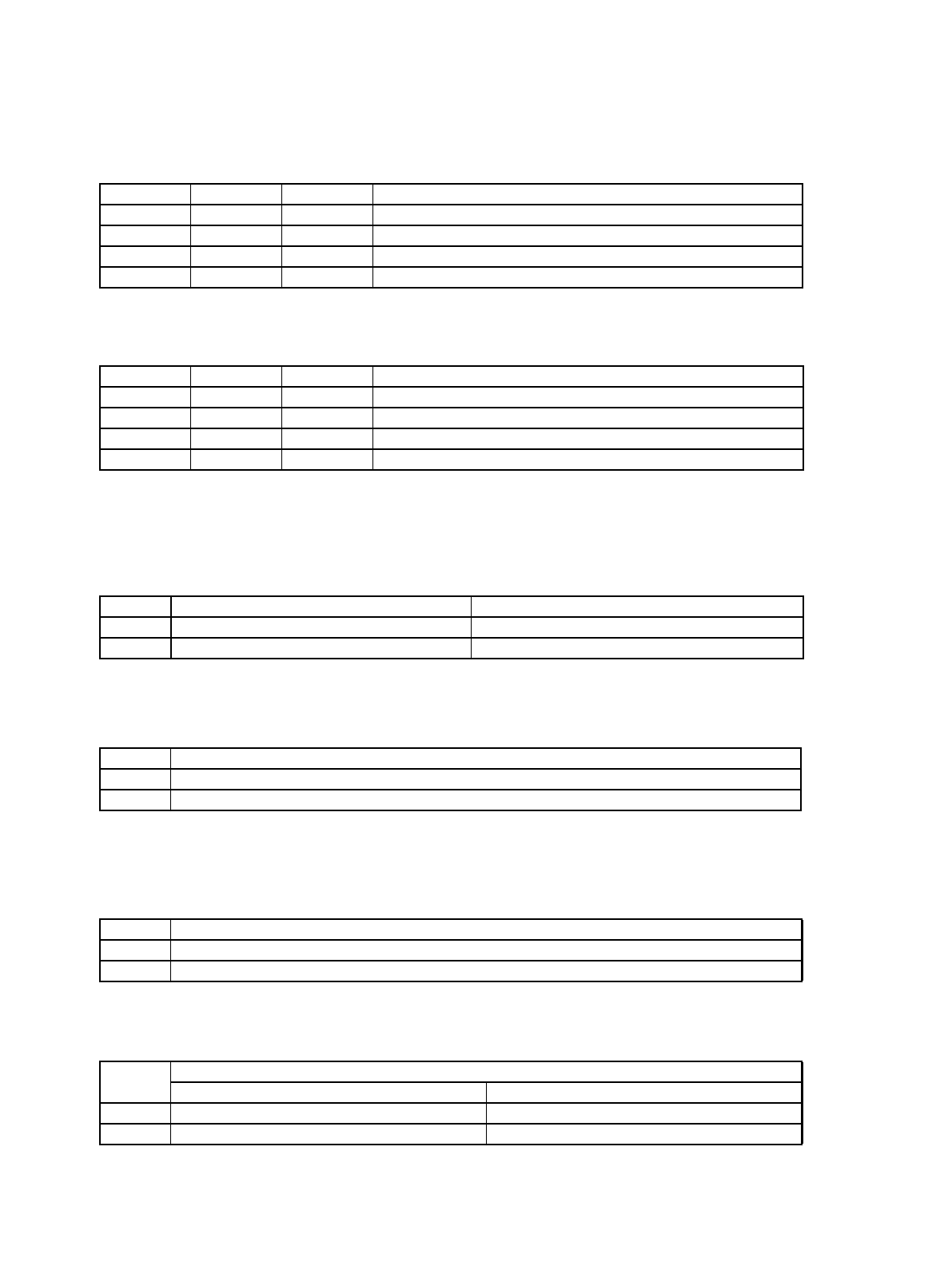

• bit9-7: Operation mode selection

Reload trigger when internal clock is selected

When the selected reload trigger is input, the value of reload register TMRLR is loaded to the down counter and the

count operation is started.

Count trigger when external event is selected

Counts an external event using the selected count trigger.

Always set MOD2 to “0”. The read value is the written value.

• bit6: Undefined

Writing has no effect on the operation. The read value is “0”.

• bit5: Output level setting

• During one-shot mode, a pulse is output during the count, and during reload mode a toggle is output.

• For output level setting bit “0” and “1” the output level is reversed.

• bit4: Enable reload

• In reload mode, down counter underflow (0000H -> FFFFH) causes the value set to reload register

(TMRLR) to be loaded to the down counter, and the count operation continues.

• In one-shot mode, down counter underflow (0000H -> FFFFH) causes the count operation to stop.

• bit3: Enable timer interrupt requests

When timer interrupt requests are enabled, the timer interrupt request flag (UF) becomes “1” and interrupt requests are

generated.

• bit2: Timer interrupt request flag

Upon down counter underflow (0000H -> FFFFH) generation, the timer interrupt request flag becomes “1”. If the

MOD2 MOD1 MOD0 Reload trigger

0 0 0 Software trigger

0 0 1 External trigger (rising edge)

0 1 0 External trigger (falling edge)

0 1 1 External trigger (both edges)

MOD2 MOD1 MOD0 Count trigger

0 0 0 --------

0 0 1 External trigger (rising edge)

0 1 0 External trigger (falling edge)

0 1 1 External trigger (both edges)

OUTL One-shot mode (RELD=“0”) Reload mode (RELD=“1”)

0 During count “H” square wave During count start “L” toggle output

1 During count “L” square wave During count start “H” toggle output

RELD Enable reload

0 One-shot mode (reload disabled)

1 Reload mode (reload enabled)

INTE Enable timer interrupt requests

0 Disable interrupt requests

1 Enable interrupt requests

UF

Timer interrupt request flag

When read When write

0 Underflow not present Clear interrupt requests

1 Underflow present No effect