267

Chapter 19 Timebase Timer

5.Operation

5. Operation

Timebase timer operation is described.

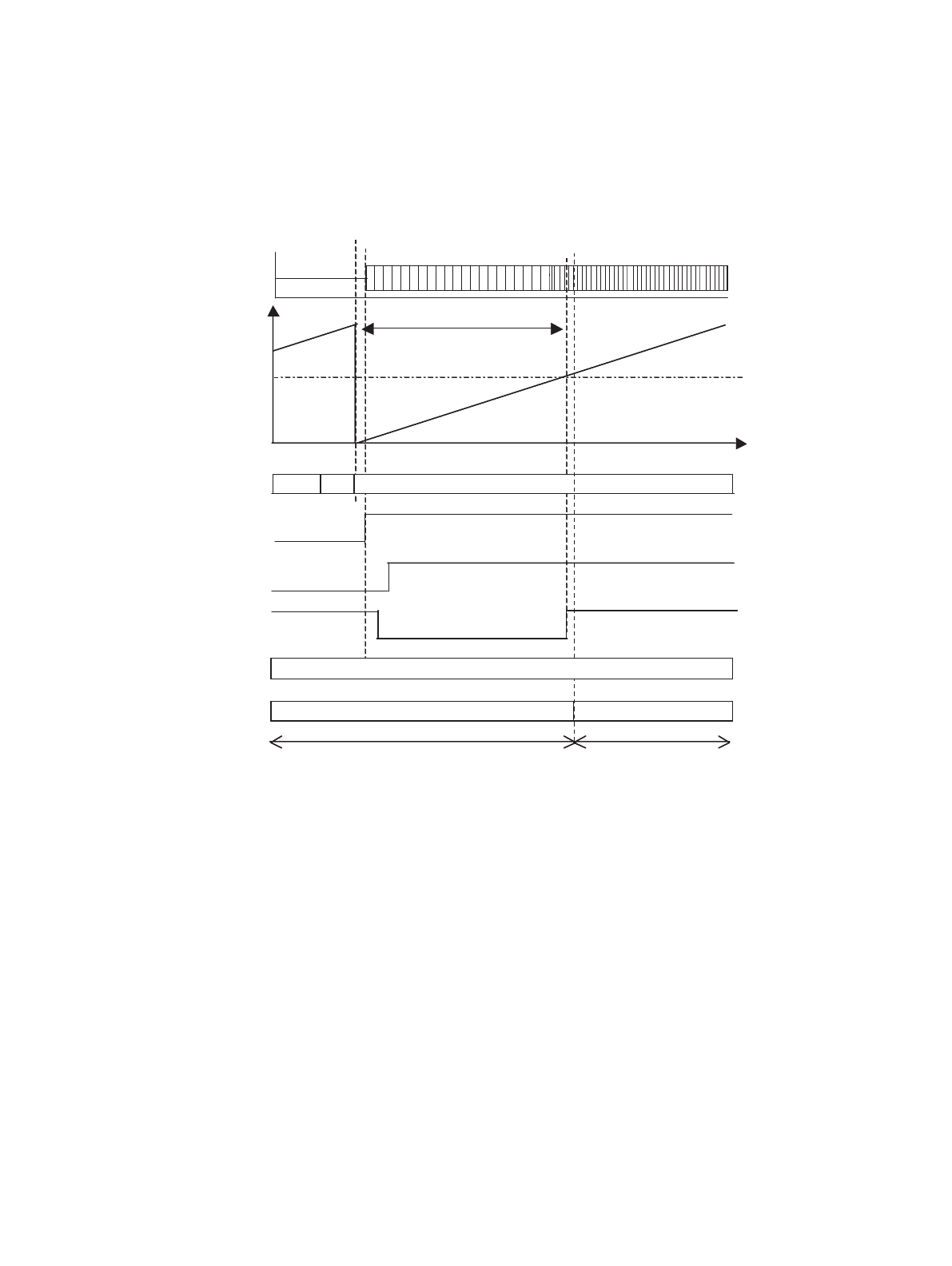

5.1 Timebase Timer Interrupt Example (Main PLL Lock Wait)

(1) Selecting the interval value in the timebase timer

(2) Selecting the main PLL value (Setting / Switching)

(3) Writing data in the timebase counter clear register in the order of “A5” and “5A”

(4) Writing “5A” clears the timebase counter and causes the count to start from”0”

(5) Enables the main PLL to operate

(6) Clears the timebase timer interrupt request using the software

(7) Setting the timebase timer interrupt request enable bit to “1”

(8) The main PLL locks

(9) A timebase timer interrupt occurs when the timebase timer interval time has elapsed

(10)Setting the main PLL to the operation clock

(3)

Time

000h

Example of

the Main PLL

oscillation

(2)

Clock switching (CLKS[1:0])

Main PLL lock wait

by the timebase timer

2

11

(4)

(6)

(CTBR)

“0 0 ” “1 0 ”

(5)

“A5 ” ”

Main PLL enable (PLL1EN)

Timebase timer interrupt

request enable (PLL1EN)

Timebase timer interrupt

request (PLL1EN)

(8)

(5)

(7)

(9)

(10)

Operation with the 2-dividing main clock

Operation with the PLL clock

(1)

(1)

“111 ”

Main PLL value

setting/switching

(PLL1S[2:0])

(3)

Timebase

counter

count

Clears the

timebase counter

600 µsec. or more

(

(4)

“0 0 ” “1 0 ”

“A5 ” ”““A5”

(10)

“5A”

“111”

“00” “10”