428

Chapter 29 MPU / EDSU

4.Registers

This register sets the 32 bit comparison value for break point 1 of CMP0. In range mode (set with ER0) the register

value of BAD1 functions as upper address limit.

In the special case of MPE=1 and COMB=1 BAD1 is not used for the point definition. CMP0 gets its point configu-

ration then from BAD3.

This register sets the 32 bit comparison value for break point 2 of CMP1. In range mode (set with ER1) the register

value of BAD2 functions as lower address limit. In addition BAD2 could be used as mask register.

This register sets the 32 bit comparison value for break point 3 of CMP1. In range mode (set with ER1) the register

value of BAD3 functions as upper address limit.

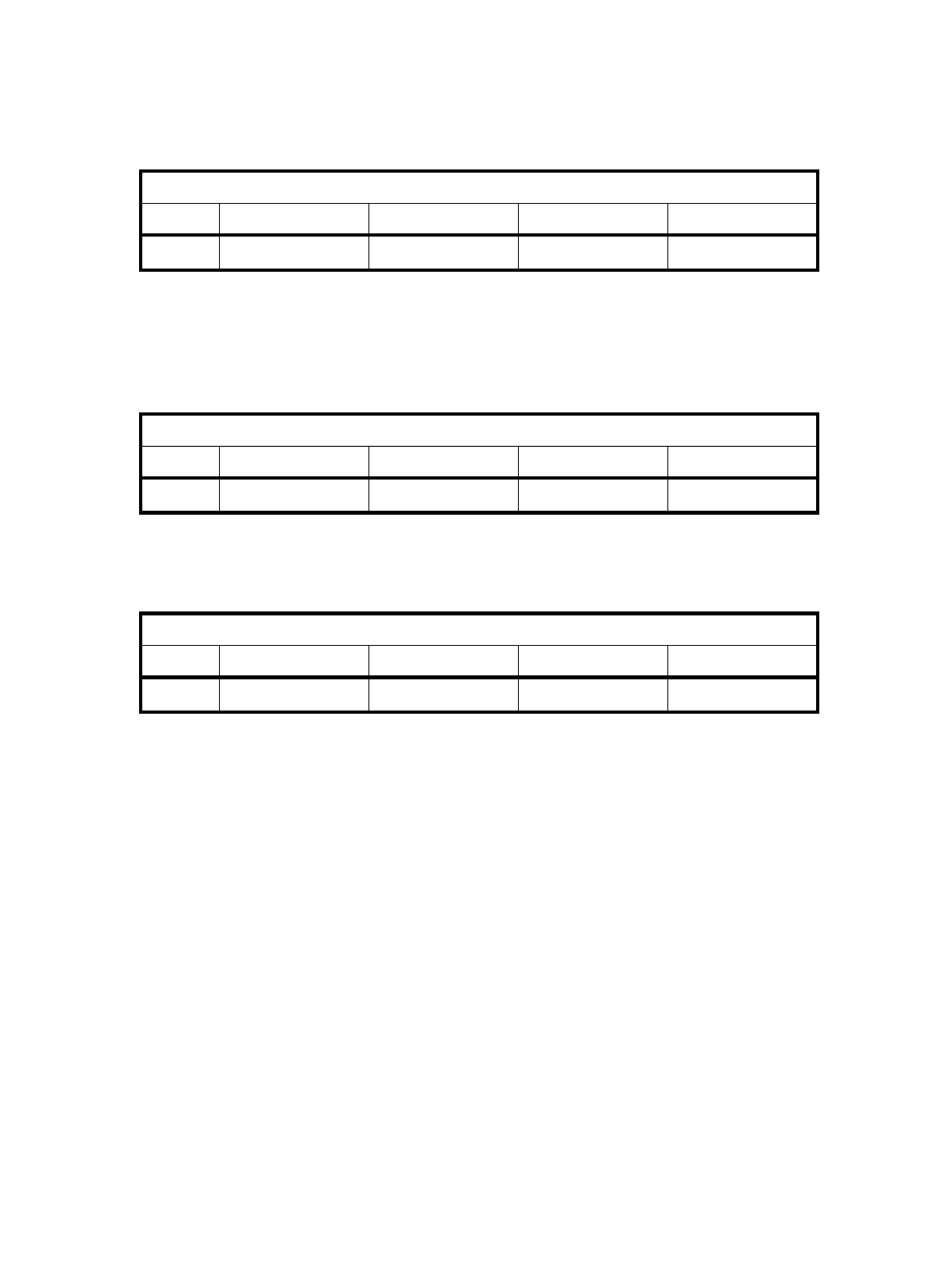

BAD1 (BAD5 BAD9, ..., BAD29) [R/W]

Address +0 +1 +2 +3

F084

H

XXXXXXXX XXXXXXXX XXXXXXXX XXXXXXXX

BAD2 (BAD6, BAD10, ..., BAD30) [R/W]

Address +0 +1 +2 +3

F088

H

XXXXXXXX XXXXXXXX XXXXXXXX XXXXXXXX

BAD3 (BAD7, BAD11, ..., BAD31) [R/W]

Address +0 +1 +2 +3

F08C

H

XXXXXXXX XXXXXXXX XXXXXXXX XXXXXXXX