350

Chapter 26 DMA Controller

2.DMA Controller (DMAC) Registers

[Bits 7 to 0] DASZ (Des Addr count SiZe)*: Transfer destination address count size specification

These bits specify the increment or decrement width for the transfer destination address (DMADA) of the

corresponding channel in each transfer operation. The value set by these bits becomes the address

increment/decrement for each transfer unit. The address increment/decrement conforms to the instruction in

the transfer destination address count mode (DADM).

• When reset: Not initialized

• These bits are readable and writable.

2.3 Transfer Source/Transfer Destination Address Setting Registers (DMASA0 to 4/

DMADA0 to 4)

The transfer source/transfer destination address setting registers (DMASA0 to 4/DMADA0 to 4)

control the operation of the DMAC channels. There is a separate register for each channel.

This section describes the configuration and functions of the transfer source/transfer destination

address setting registers (DMASA0 to 4/DMADA0 to 4).

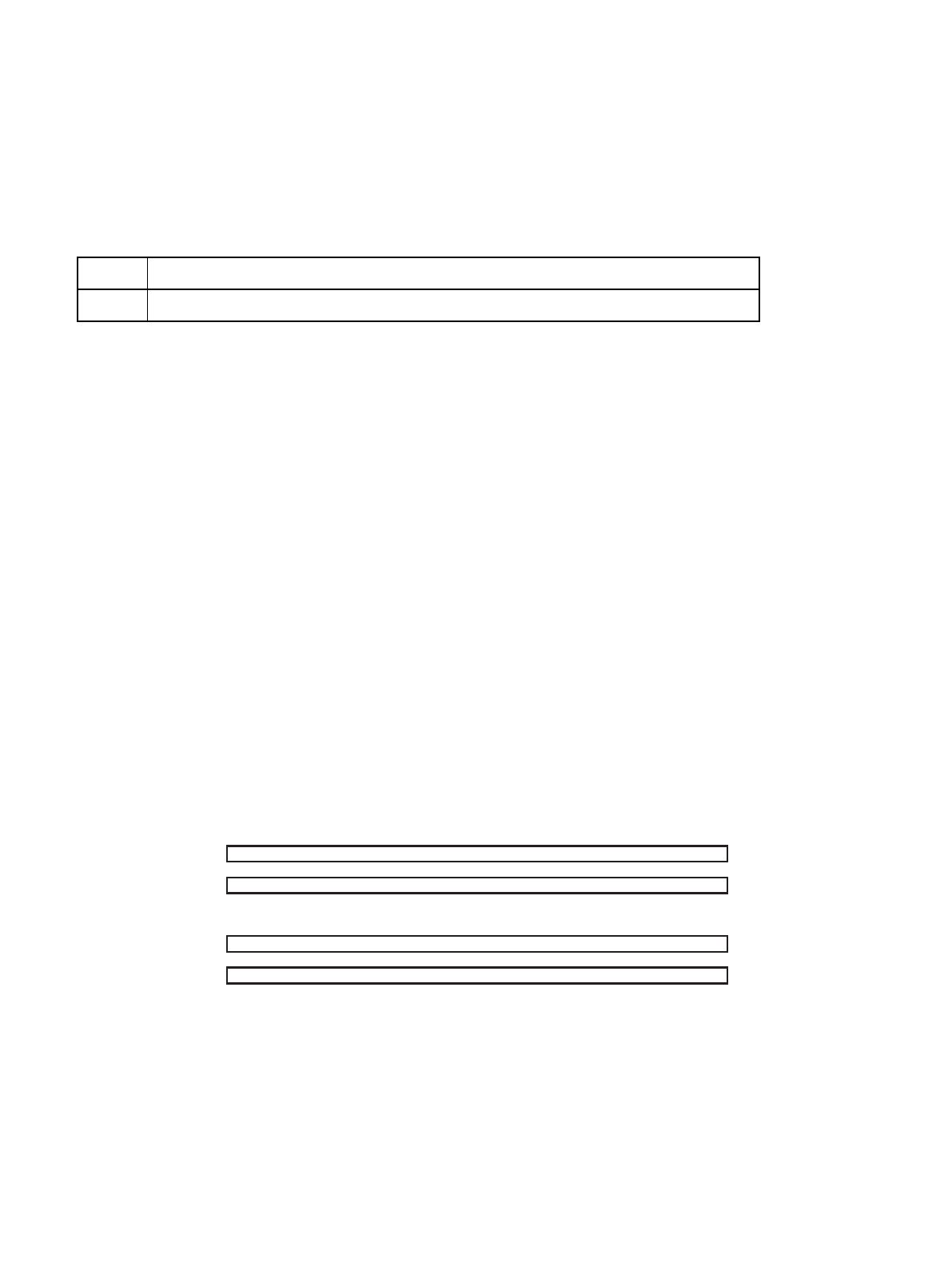

■ Bit Configuration of Transfer Source/Transfer Destination Address Setting Registers

(DMASA0 to 4/DMADA0 to 4)

The transfer source/transfer destination address setting registers (DMASA0 to 4/DMADA0 to 4) are a group of

registers that store the transfer source/transfer destination addresses. Each register is 32 bits length.

Figure 2-4"Bit Configuration of the Transfer Source/Transfer Destination Address Setting Registers (DMASA0 to

4/DMADA0 to 4)" shows the bit configuration of the transfer source/transfer destination address setting registers

(DMASA0 to 4/DMADA0 to 4).

Figure 2-4 Bit Configuration of the Transfer Source/Transfer Destination Address Setting Registers

(DMASA0 to 4/DMADA0 to 4)

Detailed Bit of Transfer Source/Transfer

Destination Address Setting Register (DMASA0 to 4/DMADA0 to 4)

The following describes the functions of the bits of each transfer source/transfer destination address setting

register (DMASA0 to 4/DMADA0 to 4).

[Bits 31 to 0] DMASA (DMA Source Addr)*: Transfer source address setting

These bits set the transfer source address.

DASZ Function

XX

H

Specify the increment/decrement width of the transfer destination address. 0 to 255

bit

bit

bit

bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

DMASA[31:16]

1514131211109876543210

DMASA[15:0]

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

DMADA[31:16]

1514131211109876543210

DMADA[16:0]

Address

001000

H

(ch0)

001008

H

(ch1)

001010

H

(ch2)

001018

H

(ch3)

001020

H

(ch4)

Address

001004

H

(ch0)

00100C

H

(ch1)

001014

H

(ch2)

00101C

H

(ch3)

001024

H

(ch4)

Initial value

XXXXXXXXXXXXXXXX

XXXXXXXXXXXXXXXX

B

XXXXXXXXXXXXXXXX

XXXXXXXXXXXXXXXX

B

Initial value