588

Chapter 31 External Bus

9.SDRAM/FCRAM Interface Operation

● Using 8 - bit SDRAM/FCRAM (Big endian)

Total data bus width of 32 bits: Use four SDRAM/FCRAM modules.

Total data bus width of 16 bits: Use two SDRAM/FCRAM modules.

Figure 9-7 shows how to use 64 - Mbit SDRAM (one bank address and 12 row addresses).

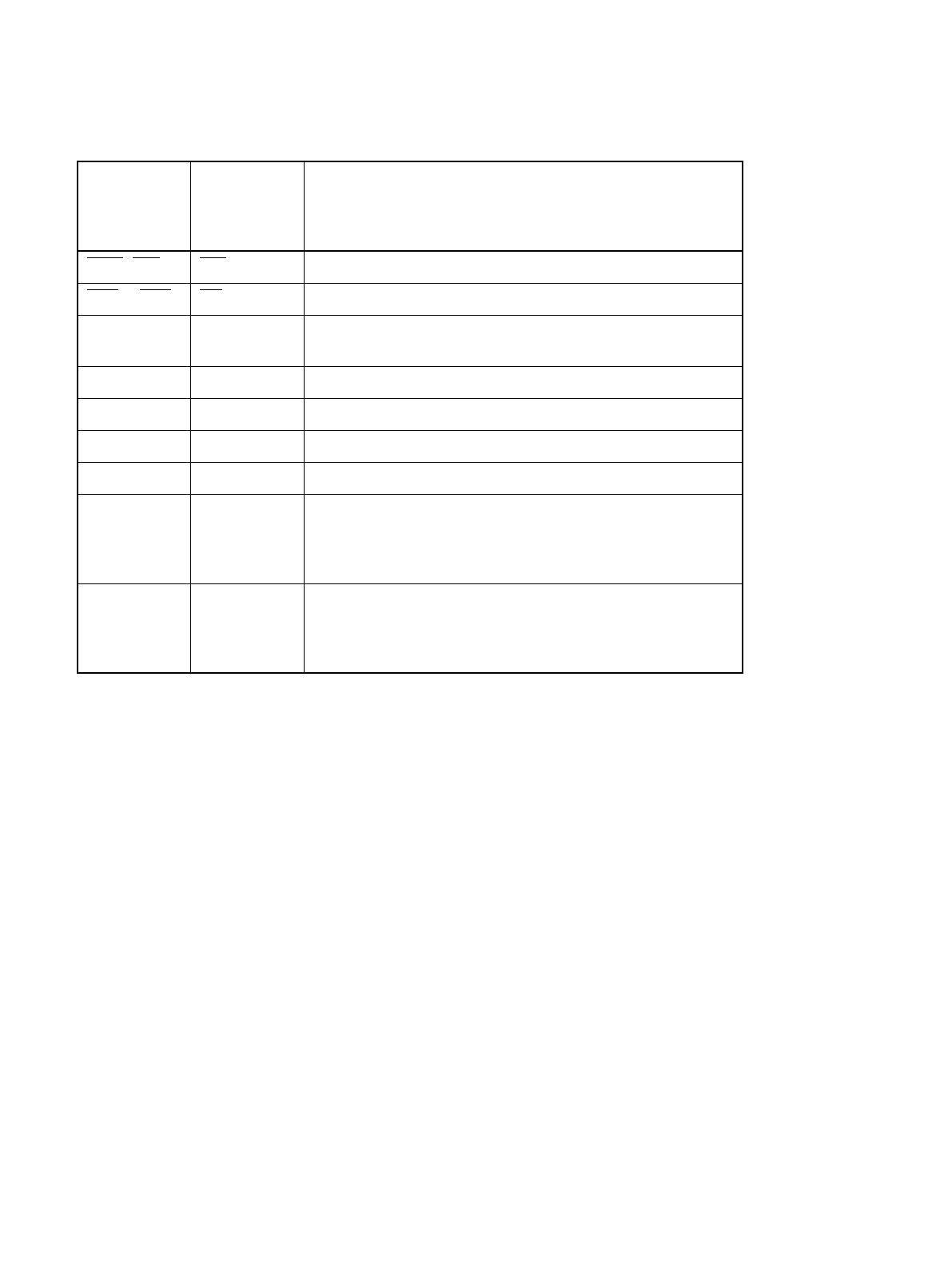

SWE (WR) WE

CS0 to CS7 CS All chip select areas can be set as SDRAM/FCRAM space.

A0 to A9 A0 to A9 Addresses do not have to be shifted depending on the bus

width.

A10/AP A10/AP A10 for row address output; otherwise AP

A11 to A13 A11 to A13 Connected to the address used for SDRAM/FCRAM.

A14 BA0 BA for 2 bank product

A15 BA1 The pin is not used for a two - bank module.

D31 to D0 DQ The connection changes depending on the endian method

and data bus width.

For detailed connection, see Section " 4. Endian and Bus

Access " .

DQMUU,

DQMUL,

DQMLU,

DQMLL

DQM The connection changes depending on the endian method

and data bus width.

For detailed connection, see Section " 4. Endian and Bus

Access " .

Table 9-1 SDRAM/FCRAM Interface to SDRAM/FCRAM Connection Table

SDRAM/

FCRAM

interface

pin

SDRAM/

FCRAM pin

Remarks