342

Chapter 26 DMA Controller

2.DMA Controller (DMAC) Registers

• When reset: IS4-0 is initialized to 00000

B

.

• When reset: EIS3-0 is initialized to 0000

B

.

• These bits are readable and writable.

[Bits 19 to 16] BLK3 to 0 (BLocK size): Block size specification

These bits specify the block size for block transfer on the corresponding channel. The value specified by these

bits becomes the number of words in one transfer unit (more exactly, the repetition count of the data width

setting). If block transfer will not be performed, set 01

H

(size 1). This register value is ignored during demand

transfer. The size becomes 1.

• When reset: Not initialized.

• These bits are readable and writable.

• If 0 is specified for all bits, the block size becomes 16 words.

• During reading, the block size is always read (reload value).

[Bits 15 to 00] DTC (Dma Terminal Count register)*: Transfer count register

The DTC register stores the transfer count. Each register has 16-bit length.

All registers have a dedicated reload register. When the register is used for a channel that is enabled to reload

the transfer count register, the initial value is automatically written back to the register when the transfer is

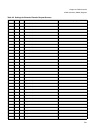

10110 0110 102 Programmable Pulse Generator 6 -

10111 0110 103 Programmable Pulse Generator 7 -

11000 0110 104 Programmable Pulse Generator 8 -

11001 0110 105 Programmable Pulse Generator 9 -

11010 0110 106 Programmable Pulse Generator 10 -

11011 0110 107 Programmable Pulse Generator 11 -

11100 0110 108 Programmable Pulse Generator 12 -

11101 0110 109 Programmable Pulse Generator 13 -

11110 0110 110 Programmable Pulse Generator 14 -

11111 0110 111 Programmable Pulse Generator 15 -

10000 0111 112 ADC 0 -

10001 0111 113 res. -

10010 0111 114 res. -

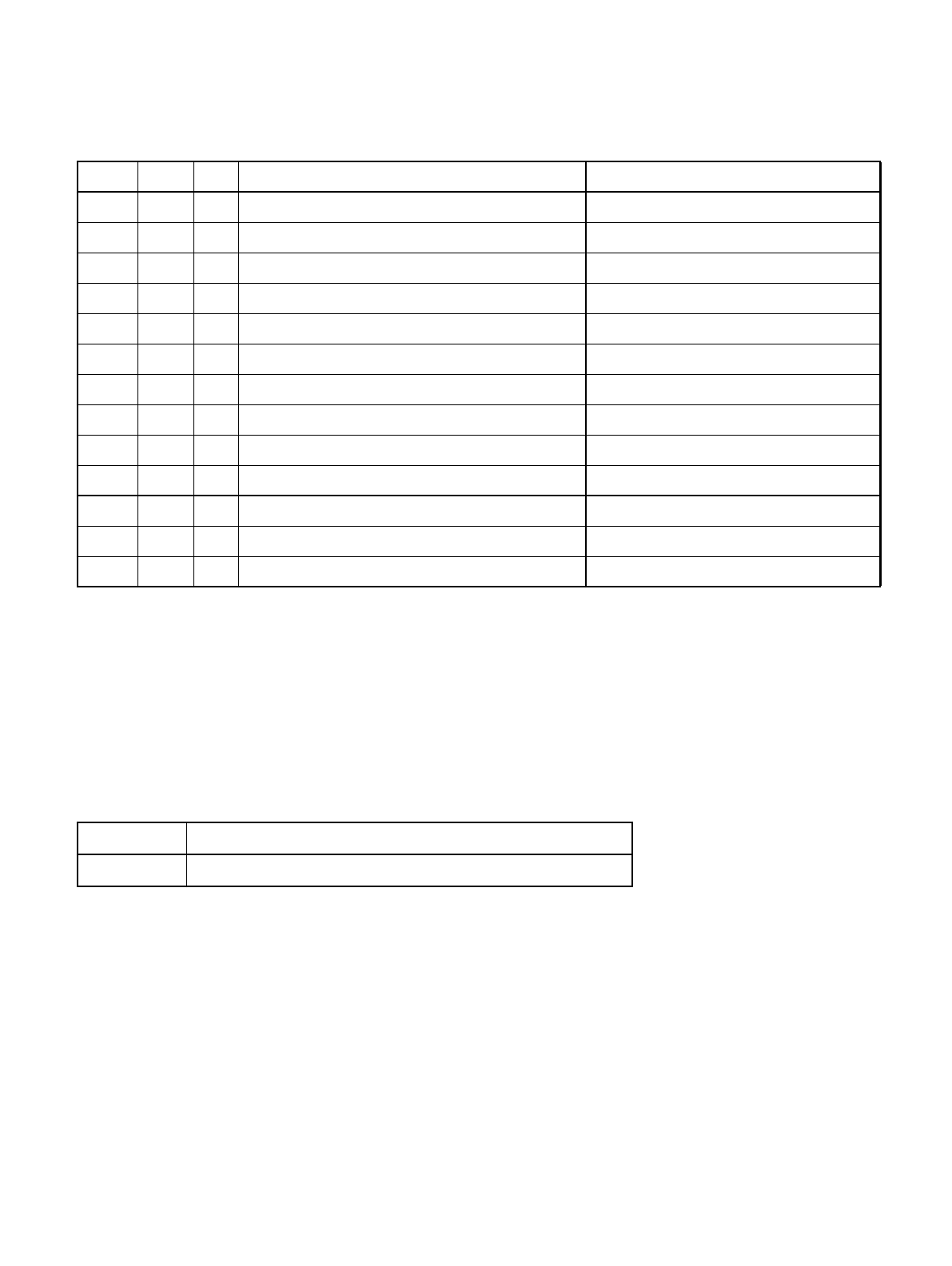

BLK Function

XXXX

B

Block size of the corresponding channel

Table 2-2 Settings for Extended Transfer Request Sources

IS EIS RN Function Transfer stop request