420

Chapter 29 MPU / EDSU

4.Registers

Group of Channels, Permission Definition Register

The permission definition registers are valid only for the group of channels operating in MPU mode. This is the case

if MPE is set to ’1’. If the group does not operate in MPU mode, the permission configuration is not required (don’t

care).

Normally MPU channels operate in range mode for the address definitions.

The type of the permission, which could be set-up, depends on the comparator type configuration (CTC) for each

comparator pair. MPU channels could be configured either to check instruction addresses (IA) or operand address-

es (OA). IA ranges could be used to define exceute permissions. OA ranges could be used to define read and write

permissions.

The comparator type for MPU usage could be set to

• CTC=0: both IA ranges define execute permissions,

• CTC=1: both OA ranges define read/write permissions and

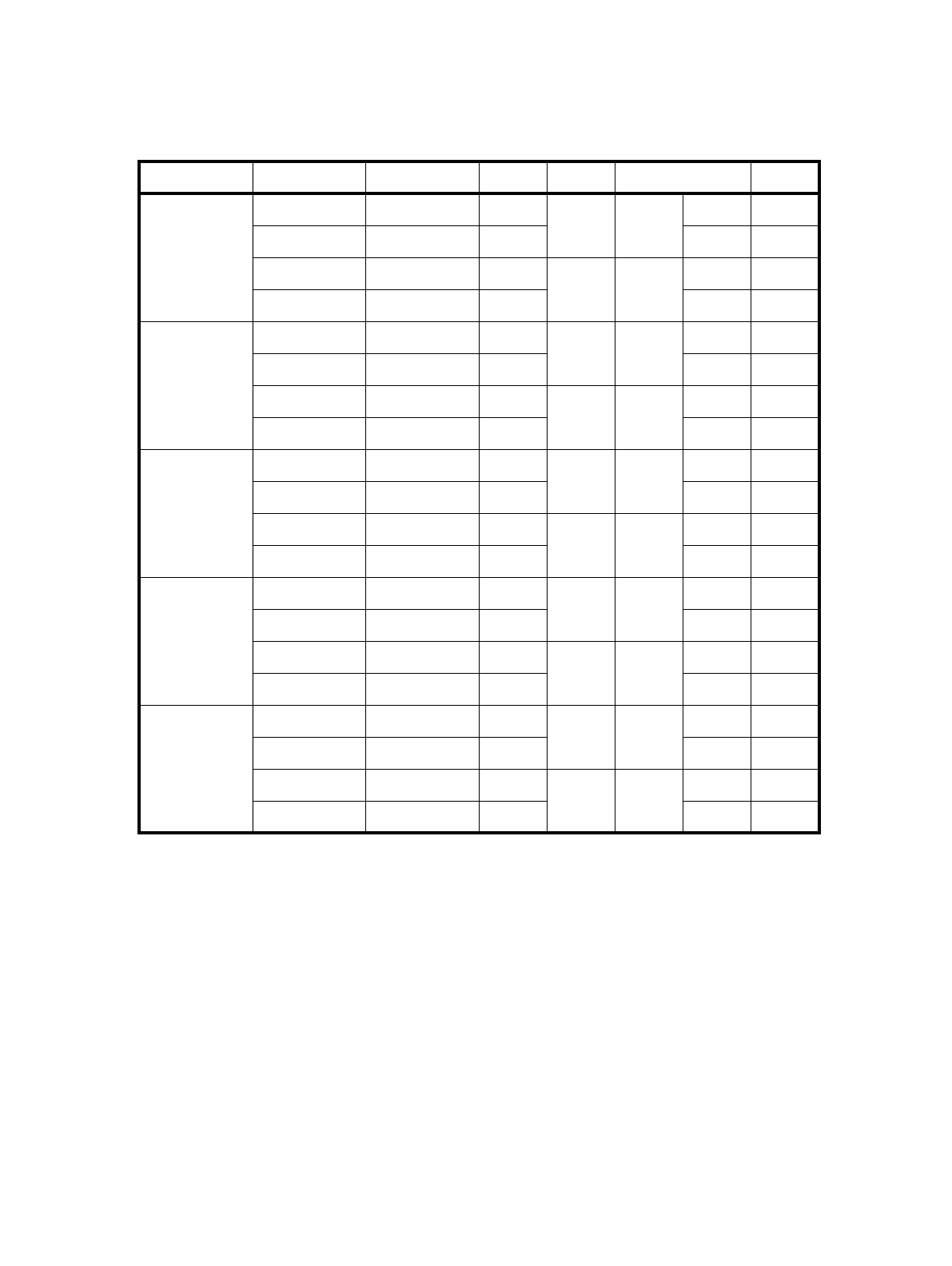

BCR3 BAD12

Point0, Mask0 EP0 EM0 range 0

ER0

OA0

BD12

BAD13

Point1 EP1

OA1

BD13

BAD14

Point2, Mask1 EP2 EM1 range 1

ER1

DT0

BD14

BAD15

Point3 EP3

DT1

BD15

BCR4 BAD16

Point0, Mask0 EP0 EM0 range 0

ER0

OA0

BD16

BAD17

Point1 EP1

OA1

BD17

BAD18

Point2, Mask1 EP2 EM1 range 1

ER1

DT0

BD18

BAD19

Point3 EP3

DT1

BD19

BCR5 BAD20

Point0, Mask0 EP0 EM0 range 0

ER0

OA0

BD20

BAD21

Point1 EP1

OA1

BD21

BAD22

Point2, Mask1 EP2 EM1 range 1

ER1

DT0

BD22

BAD23

Point3 EP3

DT1

BD23

BCR6 BAD24

Point0, Mask0 EP0 EM0 range 0

ER0

OA0

BD24

BAD25

Point1 EP1

OA1

BD25

BAD26

Point2, Mask1 EP2 EM1 range 1

ER1

DT0

BD26

BAD27

Point3 EP3

DT1

BD27

BCR7 BAD28

Point0, Mask0 EP0 EM0 range 0

ER0

OA0

BD28

BAD29

Point1 EP1

OA1

BD29

BAD30

Point2, Mask1 EP2 EM1 range 1

ER1

DT0

BD30

BAD31

Point3 EP3

DT1

BD31

Table 4-3 Relationship of BCR, BAD and BIRQ registers

Group Config Address/Data BADx Usage Point Mask Combination BIRQ