628

Chapter 32 USART (LIN / FIFO)

4.USART Registers

4.4 Reception and Transmission Data Register (RDR04 / TDR04)

The reception data register (RDR04) holds the received data. The transmission data register (TDR04) holds

the transmission data. Both RDR04 and TDR04 registers are located at the same address.

(Note) TDR04 is a write-only register and RDR04 is a read-only register. These registers are located in the

same address, so the read value is different from the write value. Therefore, instructions that perform

a read-modify-write (RMW) operation, such as the INC/DEC instruction, cannot be used.

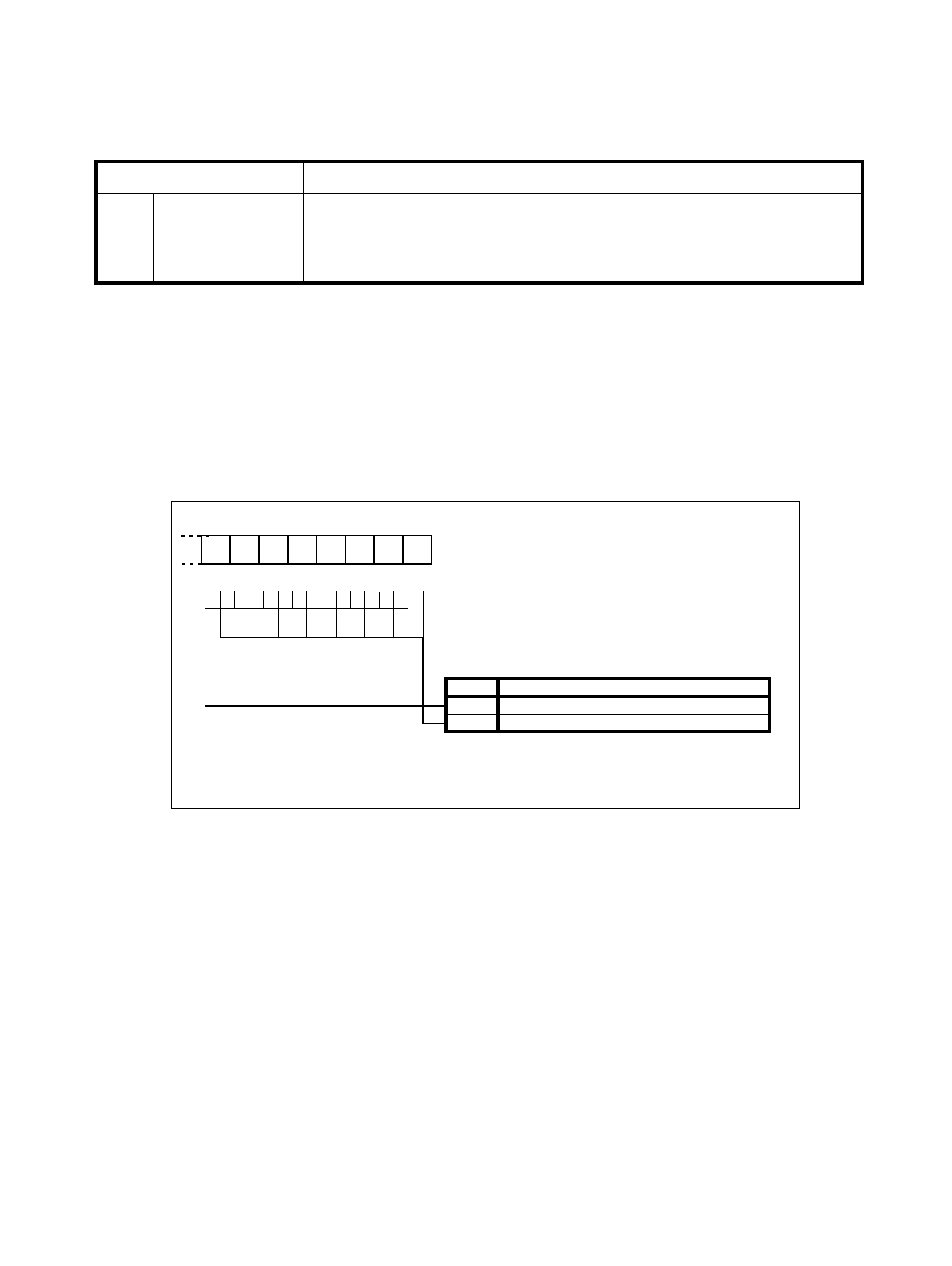

Figure 4-4 Transmission and Reception Data registers 04 (RDR04 / TDR04)

■ Reception:

RDR04 is the register that contains reception data. The serial data signal transmitted to the SIN04 pin is

converted in the shift register and stored there. When the data length is 7 bits, the uppermost bit (D7) contains

0. When reception is complete the data is stored in this register and the reception data full flag bit (SSR04:

RDRF) is set to 1. If a reception interrupt request is enabled at this point, a reception interrupt occurs.

Read RDR04 when the RDRF bit of the status register (SSR04) is 1. The RDRF bit is cleared automatically to

0 when RDR04 is read. Also the reception interrupt is cleared if it is enabled and no error has occurred.

Data in RDR04 is invalid when a reception error occurs (SSR04: PE, ORE, or FRE = 1).

■ Transmission:

When data to be transmitted is written to the transmission data register in transmission enable state, it is

transferred to the transmission shift register, then converted to serial data, and transmitted from the serial data

output terminal (SOT04 pin). If the data length is 7 bits, the uppermost bit (D7) is not sent.

When transmission data is written to this register, the transmission data empty flag bit (SSR04: TDRE) is

cleared to 0. When transfer to the transmission shift register is complete, the bit is set to 1. When the TDRE bit

is 1, the next part of transmission data can be written. If output transmission interrupt requests have been

bit8 TIE: Transmission

interrupt request

enable bit

• This bit enables or disables output of a request for transmission interrupt

to the CPU.

• A transmission interrupt request is output when this bit and the TDRE bit

are 1.

Table 4-5 Functions of each bit of status register 04 (SSR04)

Bit name Function

Initial value

0 0 0 0 0 0 0 0

B

R/W R/W R/W R/W R/WR/W R/W R/W

bit8-0

R/W Data Registers

Read Read from Reception Data Register

Write Write to Transmission Data Register

R/W : Readable and writable

76543210