684

Chapter 33 I2C Controller

2.I2C Interface Registers

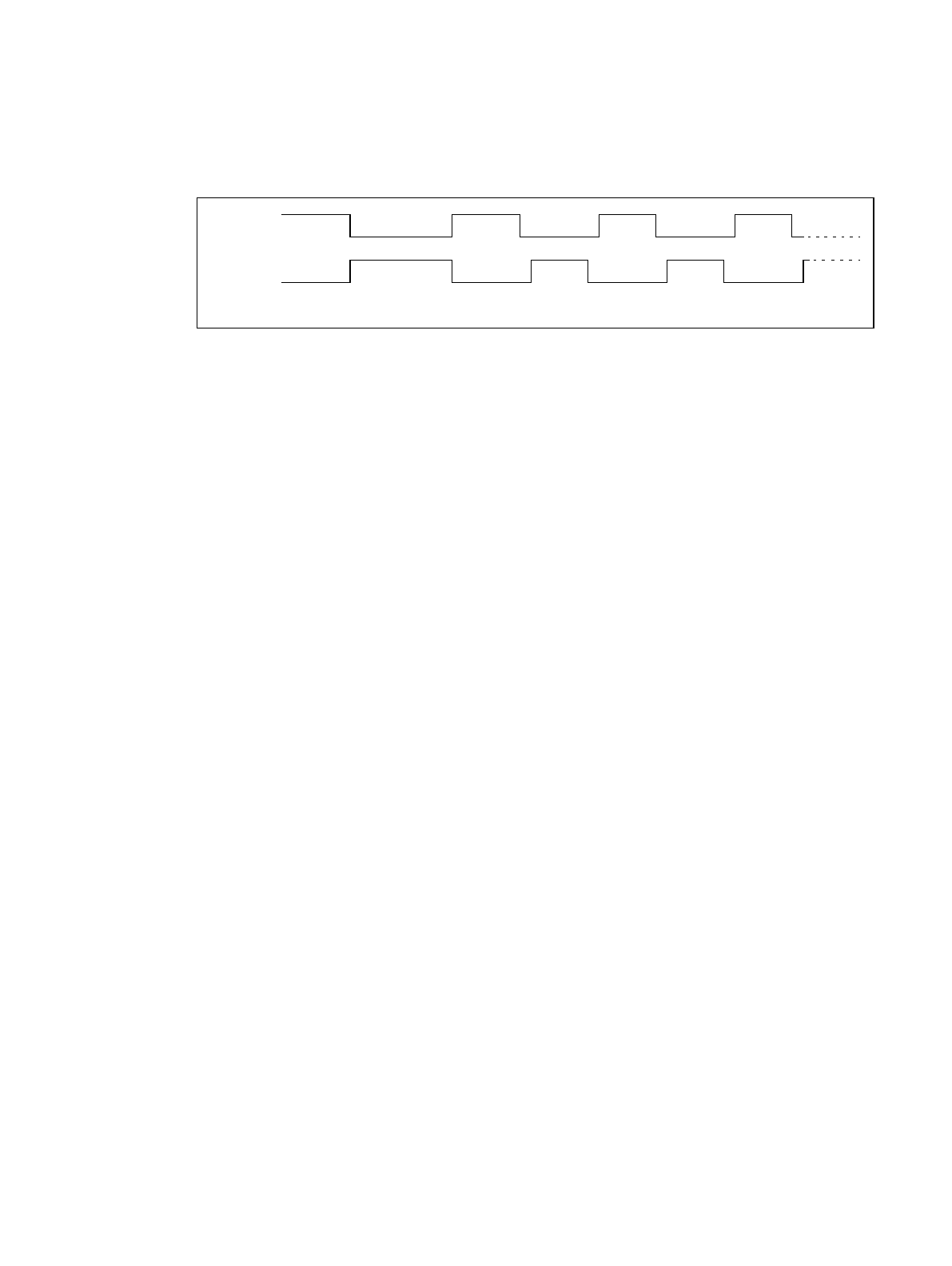

■ SCL Waveforms

Figure 2-1 SCL Waveforms

Figure 2-1 shows the SCL waveform for sending of address and data bits. The timings given in

the figure are prescaler periods (e.g. ‘9’ means 9 times the prescaler count based on the R-Bus

clock). The timings in the figure are only valid if no other device on the I2C bus influences the

SCL timing.

Address sending

Data sending

9

9

6

757

57

Time unit: Prescaler cycles

57

57